前言

本教材仍在撰写和调整中

第零章:环境配置与预备知识

0.1 硬件平台介绍

飞腾派开发板硬件平台详解

飞腾派是由萤火工场研发的国产自主可控开源硬件平台,定位于工业控制、嵌入式开发及教育领域,兼具高性能与丰富外设接口,适配多种操作系统生态。

1. 处理器与架构

- 核心配置:搭载飞腾定制四核处理器,采用ARM v8指令集,包含:

- 2×FTC664核(主频1.8GHz)

- 2×FTC310核(主频1.5GHz)

- 架构特性:

- 支持大小核协同调度

- 集成硬件虚拟化支持

- 适用于实时操作系统(RTOS)及边缘计算任务

2. 内存与存储

- 内存:

- 板载64位DDR4内存

- 提供2GB/4GB双版本

- 注:4GB版本采用鑫存储颗粒,2GB版本采用兆易创新颗粒

- 存储:

- 支持MicroSD卡或eMMC模块启动

- 默认从SD卡加载系统

- 推荐使用≥16GB容量的存储介质

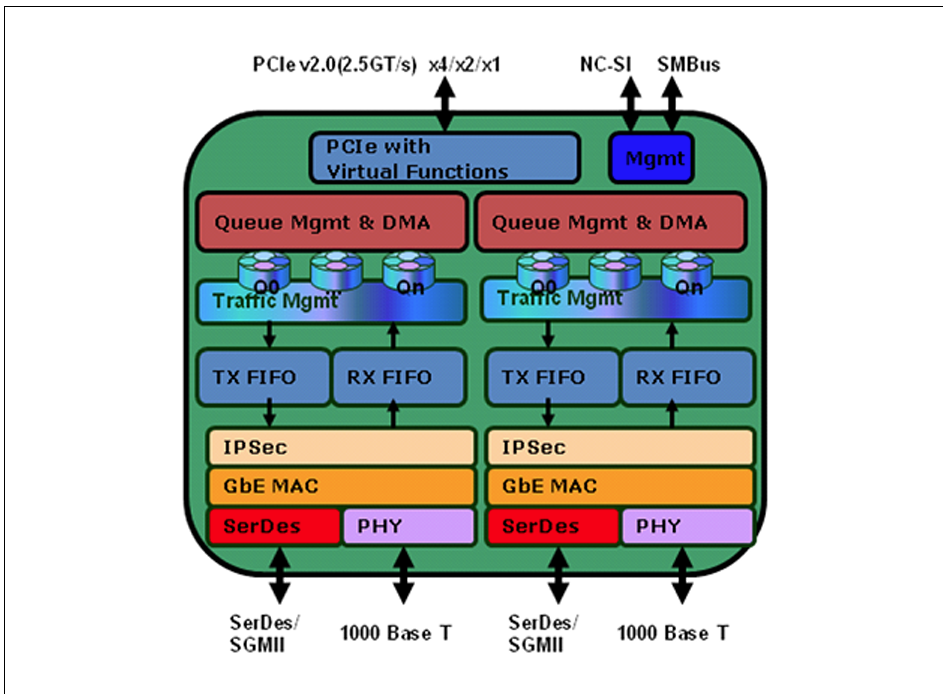

3. 网络与无线连接

- 有线网络:

- 双路千兆以太网接口(RJ45)

- 支持DHCP自动分配IP或静态配置

- 无线通信:

- 板载WiFi 6(2.4G/5G双频)

- 蓝牙4.2/BLE4.2

- 集成陶瓷天线

- 移动网络扩展:

- 通过Mini-PCIe接口可扩展4G/5G通信模组

4. 扩展接口与多媒体能力

高速接口

- Mini-PCIe×1:支持AI加速卡(如NPU模块)、4G/5G模组等扩展

- USB接口:

- USB 3.0 Host×1

- USB 2.0 Host×3

工业接口

- CAN FD×2:用于工业总线通信

- UART调试口×2

- MIO(多功能IO)×2:可配置为UART/I2C模式

- GPIO×29:支持自定义外设驱动开发

音视频输出

- HDMI:

- 最高支持1080P@60fps视频输出

- 兼容H.264/H.265硬解码

- 3.5mm音频接口:支持音频播放与录制

5. 物理规格与供电

- 尺寸:119mm × 93mm(紧凑型设计)

- 供电:

- 12V/3A直流电源

- 工作温度范围:0~50℃

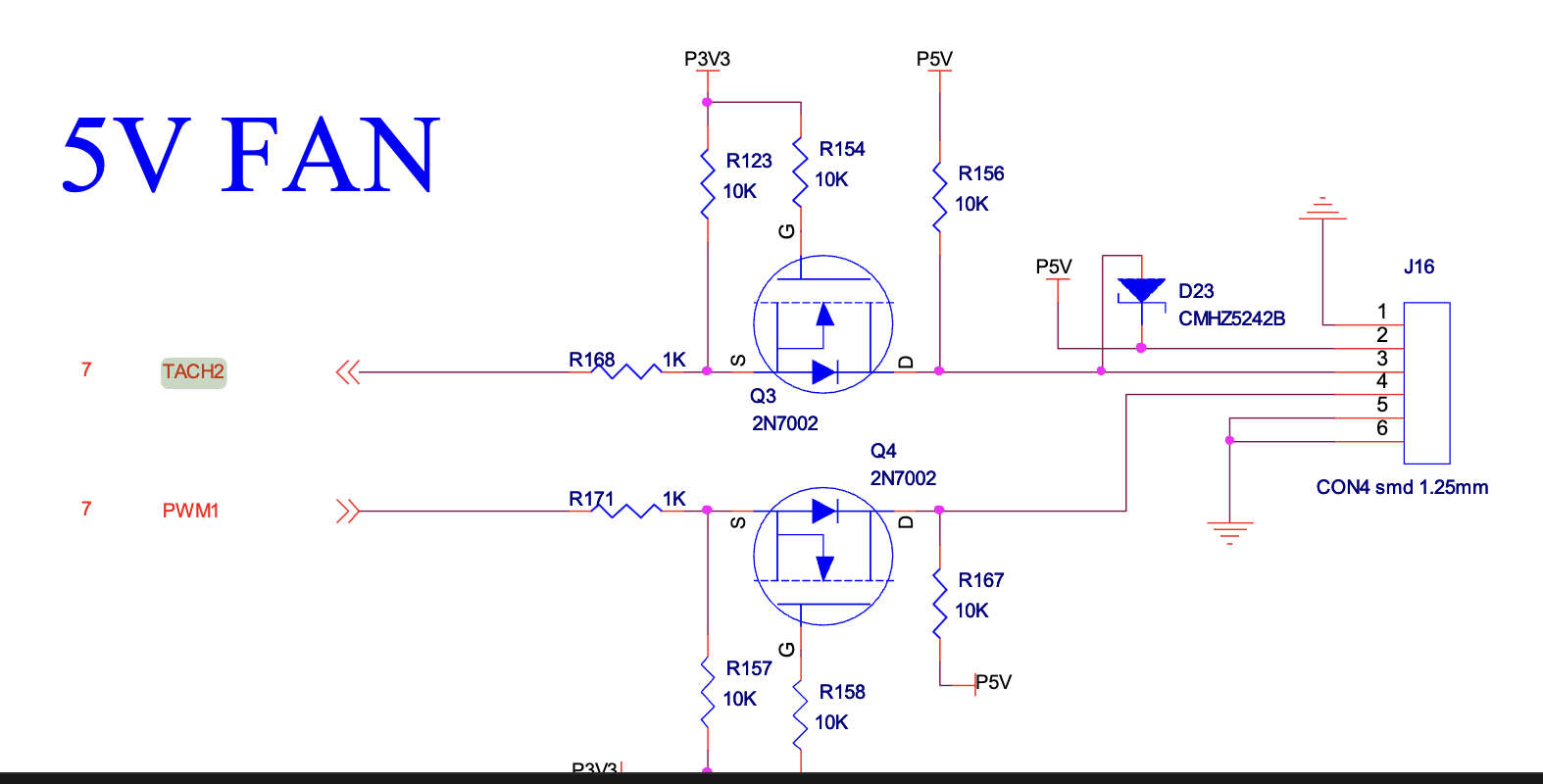

- 散热:需外接风扇(注意出风方向与电源极性)

6. 操作系统支持与开源生态

- 目前兼容系统:

- Debian 11(Phytium Pi OS)

- Ubuntu

- OpenKylin

- RT-Thread

- 开发工具链:

- Python、Qt、OpenCV等

- 适配机器视觉(如Halcon)及AI框架

- 社区资源:

- 开源硬件设计文档

- 萤火工场社区软件仓库

为何选择飞腾派进行ARCEOS驱动开发?

- 国产化适配:全国产处理器架构,符合信创场景需求

- 外设驱动全覆盖:丰富接口(CAN、I2C、SPI等)为驱动开发提供完整硬件基础

- 实时性扩展:支持Xenomai/Linux-RT,便于验证实时任务调度性能

硬件资源参考:

萤火工场官方文档

0.2 开发环境准备

0.2.1 运行环境

编译环境

编译依赖ubuntu操作系统,使用的winodws操作系统的同学可以通过安装WSL(linux 子系统)或者VMwork虚拟机来安装ubuntu。 安装好ubuntu 后需要安装必要的一些组件可直接执行如下指令

# 安装git 拉取代码

sudo apt install git

# 输入自己github的邮箱用户名

git config --global user.name "runoob"

git config --global user.email test@runoob.com

# 生成ssh密钥

ssh-keygen -t rsa -b 4096 -C "your.email@example.com"

# 安装编译qemu所需的依赖包

sudo apt install autoconf automake autotools-dev curl libmpc-dev libmpfr-dev libgmp-dev \

gawk build-essential bison flex texinfo gperf libtool patchutils bc \

zlib1g-dev libexpat-dev pkg-config libglib2.0-dev libpixman-1-dev libsdl2-dev \

git tmux python3 python3-pip ninja-build

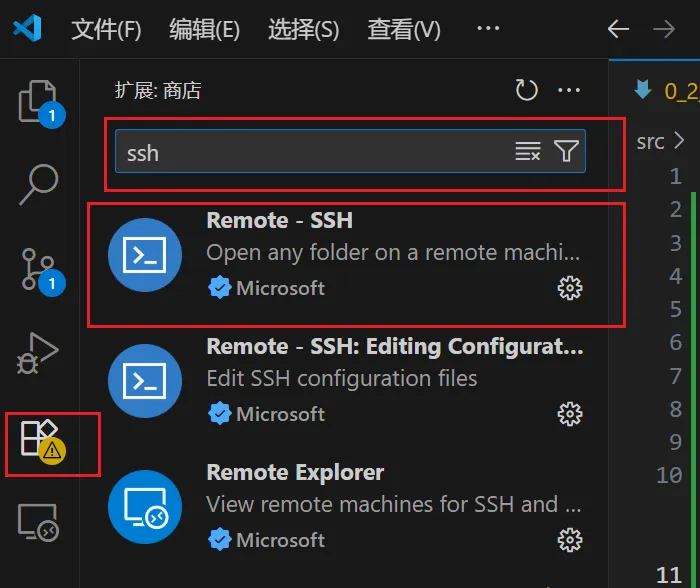

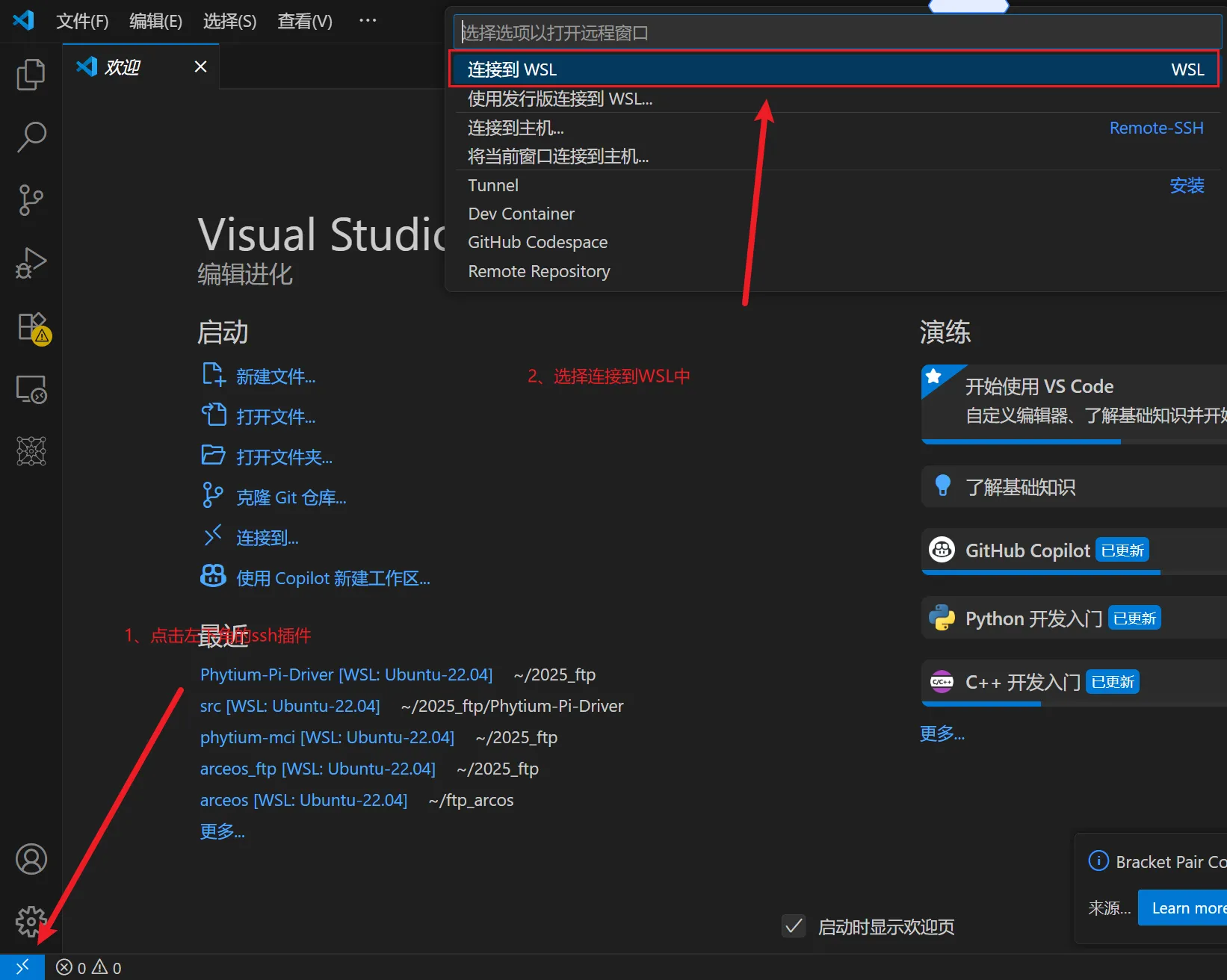

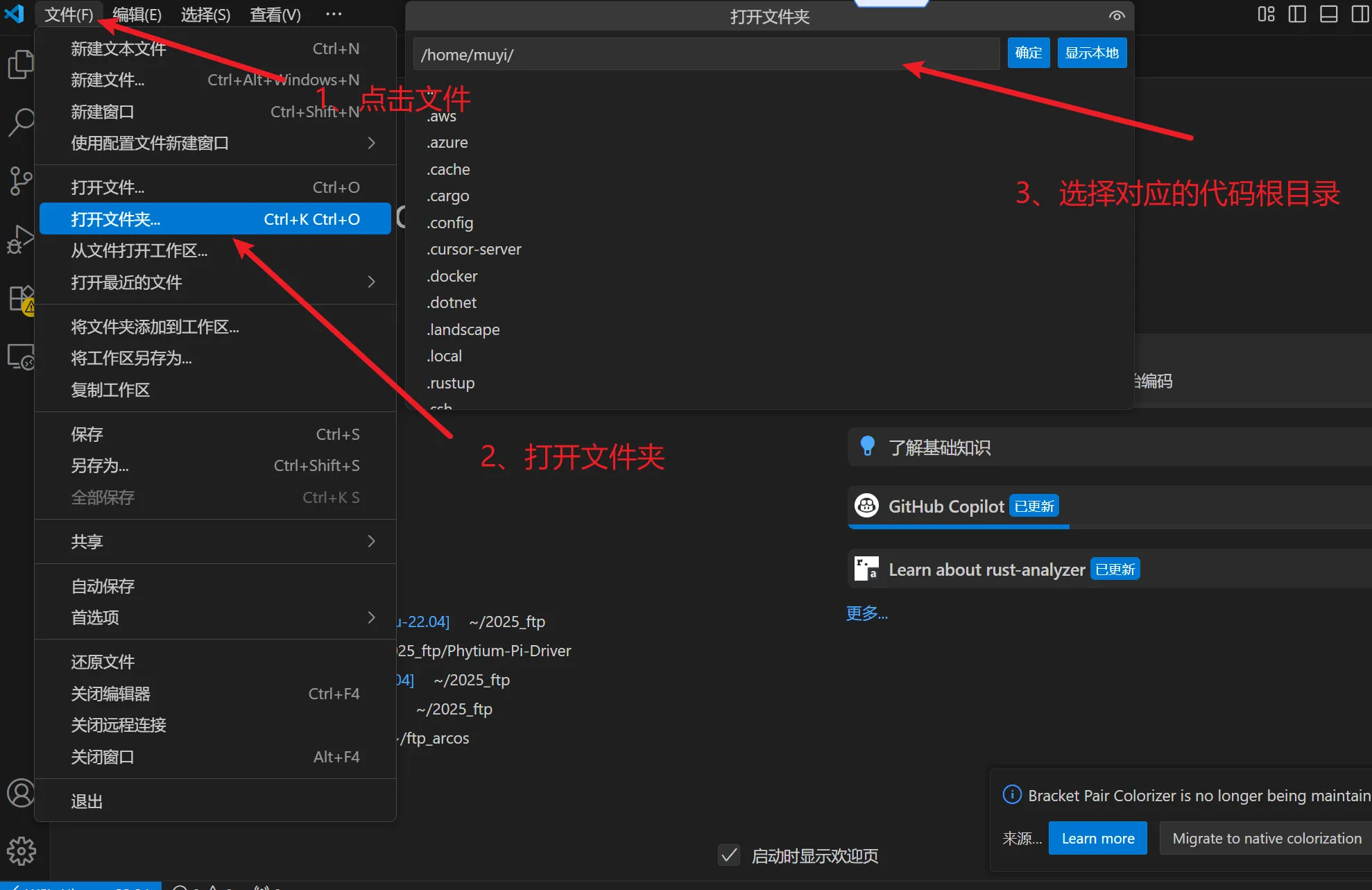

vscode使用

由于是使用的wsl(inux子系统)作为基础编译环境,默认提供的是命令行搭配vim的方式来编辑文件。这可能并不是大部分人喜欢的开发环境,所以推荐使用vscode搭配remote-ssh插件来进行开发,并且该插件对于wsl是有很好的兼容性的,安装插件后直接选择连接wsl即可使用。

qemu 补充

在第一节的指导手册上使用的qemu版本是7.0.2,而很多模拟的外设是在后续版本才加到qemu中的。所以推荐从官网安装最新版或指定版本qemu官网

以10.0.2 版本为例子,使用如下命令即可完成qemu的安装。

wget https://download.qemu.org/qemu-10.0.2.tar.xz

tar xvJf qemu-10.0.2.tar.xz

cd qemu-10.0.2

make

make install

0.2.2 飞腾派上运行Arceos

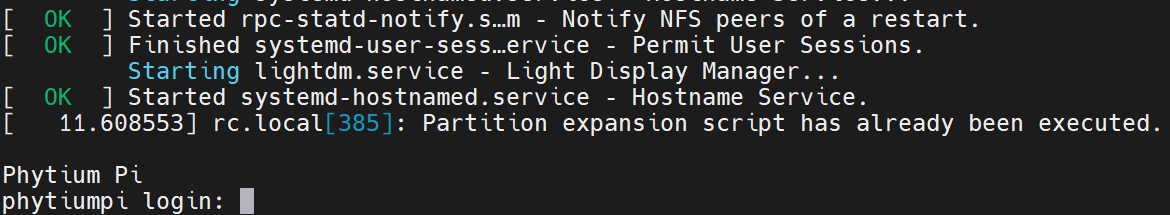

首先运行Arceos需要依赖其他系统来提供uboot,所以运行Arceos第一步是先烧录提供的飞腾派OS。

烧录飞腾派OS

飞腾派资料包(提取码:dzdv)

注释: 5-系统镜像/1-PhytiumPIOS(基于Debian)/phytiumpiosv2.1资料包/4G内存-optee版/sdcard.img.7z,解压缩。

下载解压后使用烧录工具将系统镜像烧录到TF卡,之后将TF插到飞腾派的卡槽中,最后连接电源线上电。

烧录工具推荐使用balenaEtcher也可以使用win32 disk image

注释: 常用的手机以及派上的小卡正式名叫做TF或者说microSD 大的是SD卡当然统称为sd卡也是可以的 具体区别可查看 TF卡与SD卡

注意引导方式选择从sd卡启动!!!

注释: 如果使用的是带emmc的版本可以直接从emmc启动,是当前版本的麒麟os启动会禁用风扇请注意,过热可能会损坏飞腾派。

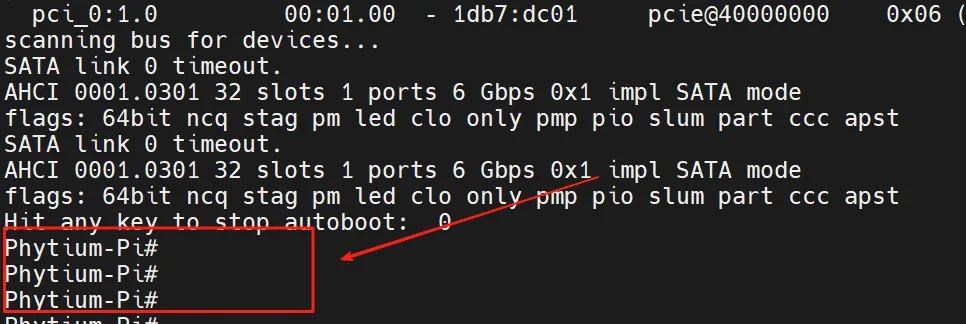

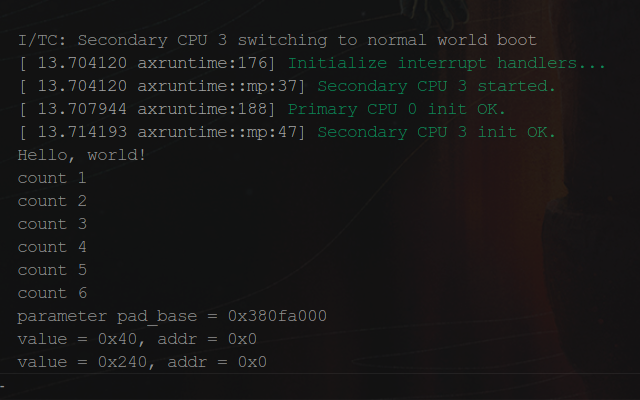

启动后连接串口,可以看到如下打印即说明系统成功启动,

账号:root

密码:root

账号:root

密码:root

编译及运行

首先快速验证请参考这个链接,可以通过ostool来快速验证当前开发环境是完整可用的,避免后面在进行了较多code后因为难以验证而放弃。

下载Arceos

git clone https://github.com/rcore-os/arceos.git

编译Arceos

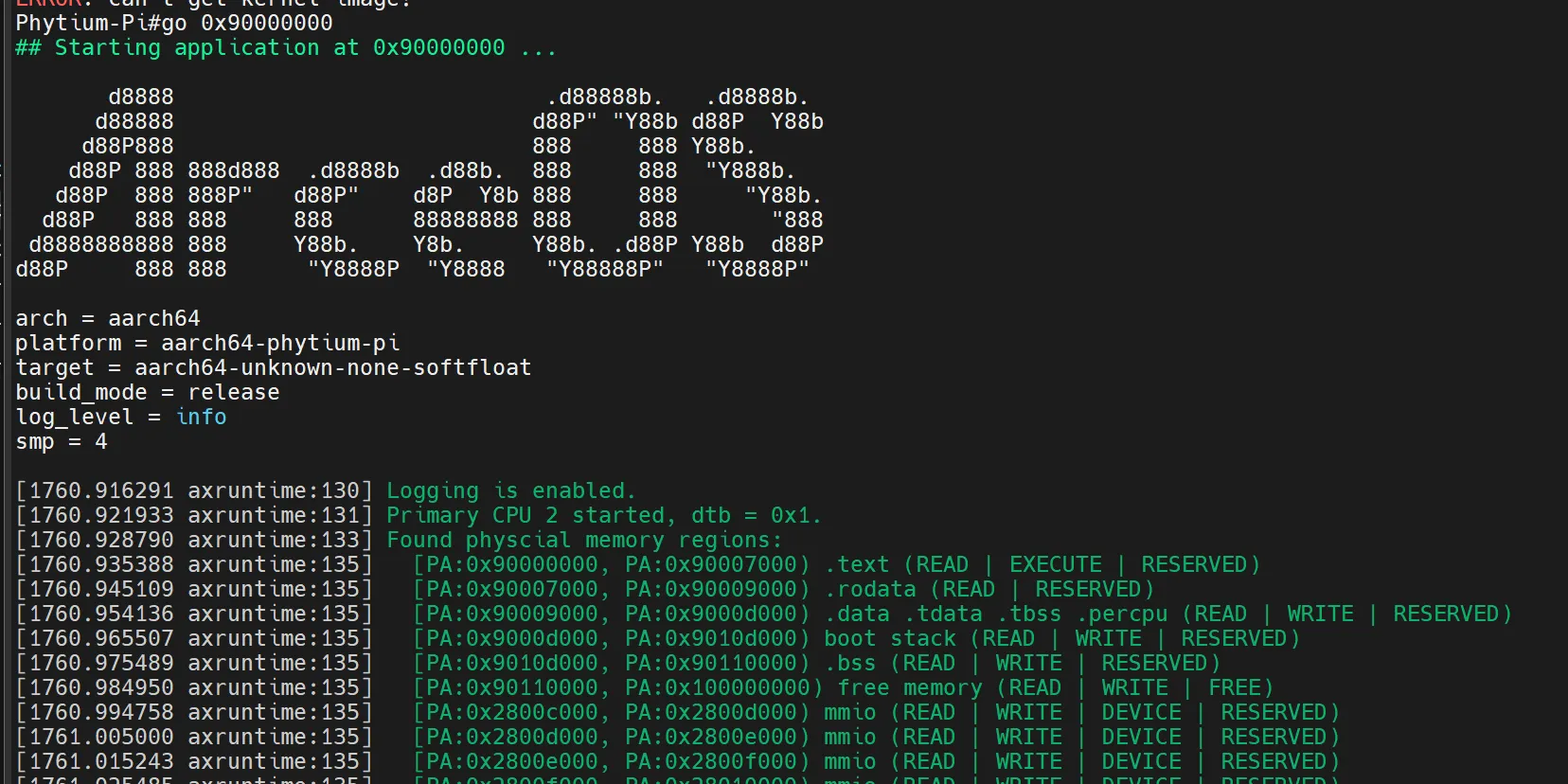

make A=examples/helloworld ARCH=aarch64 PLATFORM=aarch64-phytium-pi FEARURES="irq" SMP=4 LOG=info

之后会在example/helloword 文件夹内生成对应的可执行文件helloworld_aarch64-phytium-pi.bin

将该文件拷贝到u盘中后将u盘插入飞腾派,之后重启飞腾派并在重启过程中在串口工具中输入enter以进入cmd模式,成功进入后串口打印如下图所示。

执行如下指令即可将本地编译的Arceos部署到飞腾派上运行

usb start

fatload usb 0 0x90000000 helloworld_aarch64-phytium-pi.bin

go 0x90000000

0.2.3 飞腾派上驱动的测试

本次测试旨在全面验证 Arceos 操作系统在飞腾派开发板上各类驱动的功能正确性、稳定性及兼容性,覆盖基本外设驱动与复杂功能驱动,为后续 Arceos 系统在飞腾派平台的应用与优化提供可靠的测试依据,确保驱动程序能够满足实际嵌入式应用场景的需求。

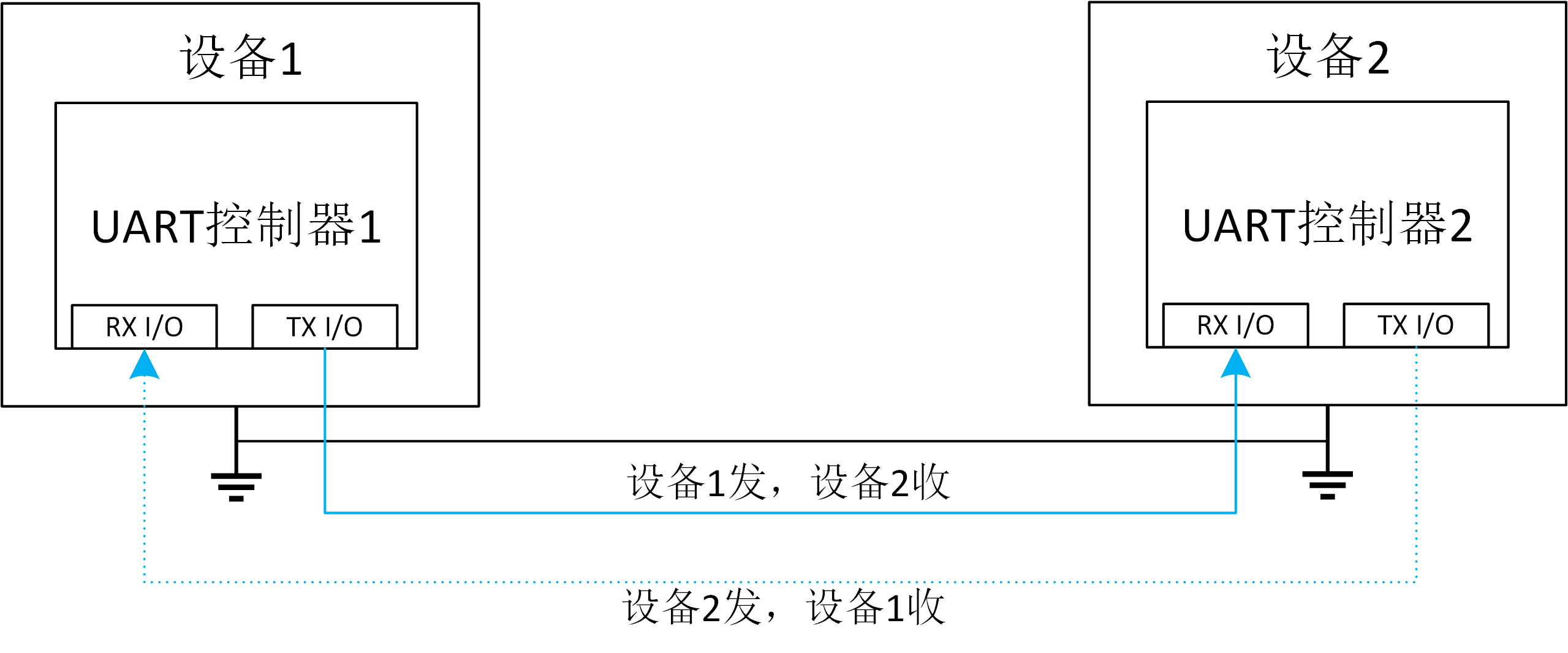

整个测试环境由两个部分组成,一个作为测试机,其上运行Linux,另一个是飞腾派(被测试开发板),其上运行Arceos。

测试机需通过 USB 转 TTL 模块 与飞腾派的 12 针调试串口连接,实现数据交互与测试控制,具体接线对应关系如下:

- 飞腾派12针接口:12pin为GND,接USB转TTL的GND

- 飞腾派12针接口:10pin为RX,接USB转TTL的TX

- 飞腾派12针接口:8pin为TX,接USB转TTL的RX

连接完成后,可通过测试机的 ls /dev/ttyUSB* 命令确认串口设备是否正常识别。

测试机上的准备

# 在测试机上运行

git clone --recursive https://github.com/shzhxh/driver-test.git

cd driver-test

make build # 编译测试镜像,生成的镜像在shell目录下

# 安装测试依赖

python3 -m venv ~/.venv

source ~/.venv/bin/activate

pip3 install -r ./scripts/requests.txt

deactivate

飞腾派上的准备

# 在测试机上运行。要求:飞腾派上已运行Linux,且与测试机在同一局域网。

scp shell/shell*.bin user@192.168.1.100:arceos.bin

# 在飞腾派上运行

sudo shutdown -r now # 重启飞腾派,按任意键进入uboot

# 在uboot下执行如下命令

ext4load mmc 0:1 0x90100000 /home/user/arceos.bin

dcache flush

go 0x90100000 # 启动Arceos

0.3 前置知识引导

本章节主要针对在飞腾派上对arceos开发驱动所需的一些前置知识进行简单的介绍

What is Arceos?

Arceos是基于组件化思想构造、以 Rust 为主要开发语言、Unikernel 形态的操作系统。与传统操作系统的构建方式不同,组件是构成 ArceOS 的基本元素。

What is Rust?

Rust 最早是 Mozilla 雇员 Graydon Hoare 的个人项目。从 2009 年开始,得到了 Mozilla 研究院的资助,2010 年项目对外公布,2010 ~ 2011 年间实现自举。自此以后,Rust 在部分重构 -> 崩溃的边缘反复横跳(历程极其艰辛),终于,在 2015 年 5 月 15 日发布 1.0 版。

-

相比 Go 语言,Rust 语言表达能力更强,性能更高。同时线程安全方面 Rust 也更强,不容易写出错误的代码。包管理 Rust 也更好,Go 虽然在 1.10 版本后提供了包管理,但是目前还比不上 Rust 。

-

相比 C++ 语言,Rust 与 C++ 的性能旗鼓相当,但是在安全性方面 Rust 会更优,特别是使用第三方库时,Rust 的严格要求会让三方库的质量明显高很多。

-

相比 Java 语言,除了极少数纯粹的数字计算性能,Rust 的性能全面领先于 Java 。同时 Rust 占用内存小的多,因此实现同等规模的服务,Rust 所需的硬件成本会显著降低。

这里是部分 Rust 学习相关资料的链接:

- Rust程序设计语言中文版(https://www.rustwiki.org.cn/zh-CN/book/ch01-02-hello-world.html)

- Rust语言圣经(https://course.rs/into-rust.html)

- Rustling(编程题库,可以在实践中对照学习具体用法,具体练习方法在仓库文档中)(https://github.com/LearningOS/rustling-25S-template)

What is Unikernel?

Unikernel 是操作系统内核设计的一种架构(或称形态),从下图对比可以看出它与其它内核架构的显著区别:

.png) Unikernel 相对其它内核架构有三个特点:

Unikernel 相对其它内核架构有三个特点:

单特权级:应用与内核都处于同一特权级 - 即内核态,这使得应用在访问内核时,不需要特权级的切换。 单地址空间:应用没有单独的地址空间,而是共享内核的地址空间,所以在运行中,也不存在应用与内核地址空间切换的问题。 单应用:整个操作系统有且仅有一个应用,所以没有多应用之间隔离、共享及切换的问题。 所以相对于其它内核架构,Unikernel 设计实现的复杂度更低,运行效率相对较高,但在安全隔离方面,它的能力最弱。Unikernel 有它适合的特定的应用领域和场景。

ArceOS 选择 Unikernel 作为起步,希望为将来支持其它的内核架构建立基础。本实验指导正是对应这一阶段,从零开始一步一步的构建 Unikernel 形态的操作系统。Unikernel 本身这种简化的设计,可以让我们暂时忽略那些复杂的方面,把精力集中到最核心的问题上。

上图就是 ArceOS 的整体架构,由apps、crates、modules组成

- apps: 应用程序。它的运行需要依赖于modules组件库。

- modules: ArceOS的组件库。

- crates: 通用的基础库。为modules实现提供支持。

本开发手册主要针对 ArceOS 在 Phytium-Pi上开发驱动进行辅助说明,因此对于apps部分不作过多说明,主要对于目前已实现的crates和modules进行说明以辅助开发人员查询

Crates

- allocator: 内存分配算法,包括:bitmap、buddy、slab、tlsf。

- arm_gic: ARM通用中断控制器 (GICv2) 。

- arm_pl011: ARM串行通信接口,用于处理器和外部设备之间的串行通信 。

- axerrno: ArceOS的错误码定义。

- axfs_devfs: ArceOS的设备(Device)文件系统,是axfs_vfs一种实现。

- axfs_ramfs: ArceOS的内存(RAM)文件系统,是axfs_vfs一种实现。

- axfs_vfs: ArceOS的虚拟文件系统接口。

- axio: no_std环境下的I/O traits 。

- capability: Capability-based security 通过设置访问权限控制对系统资源的访问。

- crate_interface: 提供一种在 crate 中定义接口(特征)的方法,其目的是解决循环依赖。

- driver_block: 通用的块存储(磁盘)驱动程序的接口定义。

- driver_common: ArceOS的通用设备驱动接口定义,包括:disk、serial port、 ethernet card、GPU。

- driver_display: 通用的图形设备驱动程序接口定义。

- driver_net: 通用的网络设备 (NIC) 驱动程序定义。

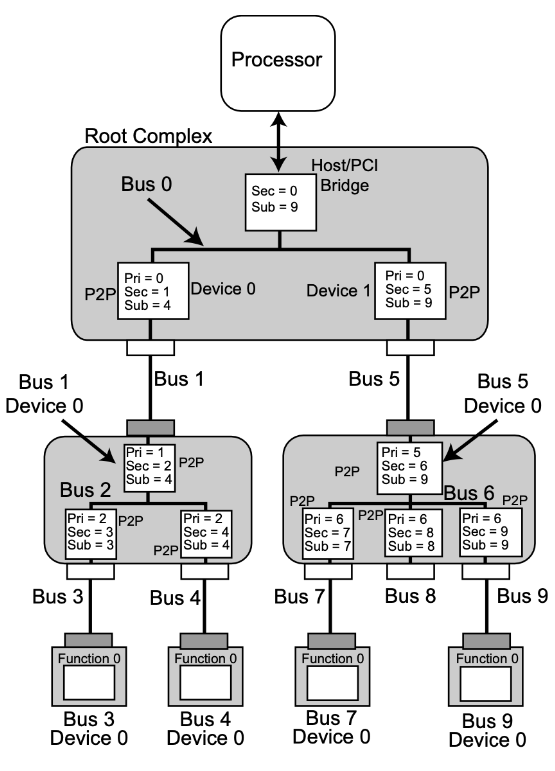

- driver_pci: 定义对PCI总线操作。

- driver_virtio: 实现在driver_common定义的驱动。

- flatten_objects: 为每个存储对象分配一个唯一的ID。

- handler_table: 无锁的事件处理程序表。

- kernel_guard: 利用RAII创建具有本地IRQ或禁用抢占的临界区,用于在内核中实现自旋锁。

- lazy_init: 延迟初始化。

- linked_list: 链表。

- memory_addr: 提供理物理和虚拟地址操作的辅助函数。

- page_table: 页表。

- page_table_entry: 页表项。

- percpu: per-CPU的数据结构。

- percpu_macros: per-CPU的数据结构的宏实现。

- ratio: 比率相关计算。

- scheduler: 统一的调度算法接口,包括:cfs、fifo、round_robin。

- slab_allocator: no_std 环境下的 Slab 分配器(一种内存管理算法)。

- spinlock: no_std 环境下的自旋锁实现。

- timer_list: 定时器,在计时器到期时触发。

- tuple_for_each: 提供遍历tuple字段的宏和方法。

crates可以在 https://crates.io/ 进行具体查询

Modules

- axalloc: ArceOS 的全局内存分配器.

- axconfig: ArceOS 特定平台编译的常量和参数配置。

- axdisplay: ArceOS 的图形化模块。

- axdma: ArceOS 中为需要直接内存访问的设备驱动提供DMA支持。

- axdriver: ArceOS 的设备驱动模块。

- axfs: ArceOS 的文件系统模块。

- axhal: ArceOS硬件抽象层,为特定平台的操作提供统一的API。

- axlog: ArceOS 多个级别日志记录宏,包括:error、warn、info、debug、trace。

- axmm: ArceOS 的内存管理模块,提供虚拟内存地址空间抽象,支持线性映射和按需分配映射

- axnet: ArceOS 的网络模块,包括:IpAddr、TcpSocket、UdpSocket、DnsSocket等。

- axns: ArceOS 中用于命名空间管理功能的模块

- axruntime: ArceOS 的运行时库,负责系统启动和初始化序列,协调其他模块的初始化过程,是应用程序运行的基础环境。

- axsync: ArceOS 提供的同步操作模块,包括:Mutex、spin。

- axtask: ArceOS 的任务调度管理模块,包括:任务创建、调度、休眠、销毁等。

值得注意的是,并非所有模块都是必需的,其中axruntime、axhal、axconfig、axlog在所有构建中都会被启用并编译,而其他模块则会根据启动的功能特性进行选择性的编译,使得ArceOS可以根据不同的需求进行定制化构建

ArceOS最新主线仓库(https://github.com/arceos-org/arceos)

Phytium-Pi

- 顶层接口视图与说明

- 底层接口视图与说明

.png.png)

第一章:硬件控制类驱动

1.1 GPIO驱动开发

1. 硬件工作原理

1.1 模块概述

- 功能描述

GPIO 是 General Purpose Input Output(通用输入/输出) 的缩写,也就意味着这种类型的外设可以配置为多种输入/输出类型。单根GPIO的模型可以简单理解为一根导线。 导线的一端留给硬件工程师,他们可以将这一端任意的连接到他们想要的地方,然后告诉驱动工程师,他们想要 ”这根线“ 起到什么作用;导线的一端连接到cpu核心,驱动工程师通过cpu配置这个模块为指定的功能。

一般来说,GPIO可以用于获取某个的高低电平,作为cpu中断触发源等等。

-

应用场景

- 外部中断源输出。连接到特定的开关上去,当这个开关被按下时,电压发生跳变,由此执行相应逻辑。

- 检测外部输入,用于检查系统关键位置是否满足要求。

- 输出恒定电压,用于点亮LED等。

-

核心特性

- 开漏输出:可以实现电平转换,输出电平取决于上拉电阻电源;可以实现io的线与逻辑。

- 推挽输出:通过控制两个晶体管的开关来控制电平状态,优点是驱动能力较强,输出IO口驱动电流最大可到20ma。

- 浮空输入:浮空输入是指将输入引脚未连接到任何外部信号源或电路,使其处于未定义的状态。

- 下拉输入:芯片输入引脚通过电阻接到电源电压。

- 上拉输入:芯片输入引脚通过电阻借到参考0电平。

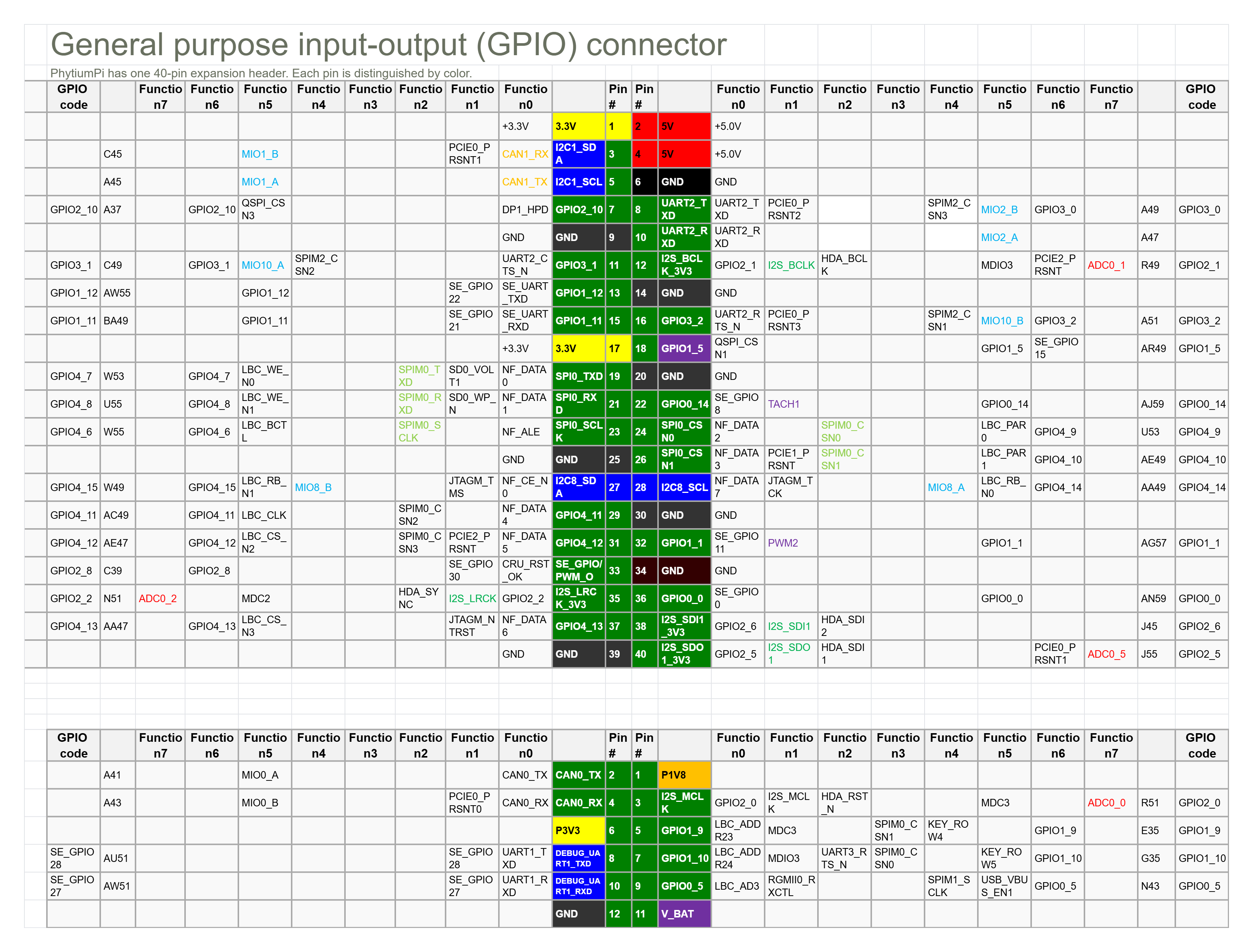

1.2 硬件接口介绍

- 扩展头:飞腾派(Phytium Pi)开发板提供 40-pin GPIO 扩展头(双排引脚,间距 2.54mm),位于板边,兼容类树莓派布局。引脚涵盖通用 GPIO、电源、GND 和专用信号(如 I2C、UART)。

- 引脚数量:最多暴露 29 个通用 GPIO(来自 6 个控制器,总 96 个信号,受板上限制)。其他引脚支持多路复用(MUX)为 I2C、SPI、UART、CAN 等。

- 电平标准:3.3V TTL 逻辑电平(高电平 >2V,低电平 <0.8V)。每个引脚最大电流约 16mA,总电流限制 50-100mA(依版本)。

- 颜色区分:

- 电源:红(3.3V/5V,Pin 1/2 等)。

- GND:黑(Pin 6/9 等)。

- GPIO:橙(e.g., Pin 7: GPIO2_10)。

- 专用信号:绿(e.g., Pin 3/5: I2C1_SDA/SCL)。

示例引脚(部分):

- Pin 7: GPIO2_10(MUX 为 UART2_TXD、DP1_HPD 等)。

- Pin 11: GPIO3_1(MUX 为 UART2_CTS_N、SPIM2_CSN2)。

- Pin 3/5: I2C1_SDA/SCL(MUX 为 CAN1_RX/TX)。

1.3 时序图

飞腾派(Phytium Pi)GPIO 设备支持异步数字输入/输出和中断触发,无固定时钟信号。以下为 GPIO 的典型时序图,展示输出控制(如 LED 点亮/熄灭)和中断触发(如按钮按下检测)。时序图基于 3.3V 电平,切换时间 <10ns,支持上升/下降沿中断。

GPIO 输出时序(LED 控制示例)

描述:驱动程序通过寄存器(如 GPIO 输出寄存器)设置引脚电平(高/低),控制外部 LED。假设使用 Pin 7(GPIO2_10)点亮/熄灭 LED。

sequenceDiagram

participant D as 驱动

participant G as GPIO控制器

participant L as LED

D->>G: 写寄存器(0x28034000,设高电平)

G->>L: 输出 3.3V(点亮)

Note over G,L: 切换时间 <10ns

D->>G: 写寄存器(设低电平)

G->>L: 输出 0V(熄灭)

GPIO 中断时序(按钮触发示例)

描述:配置 GPIO 为输入模式,启用中断(上升沿触发),检测按钮按下。假设使用 Pin 11(GPIO3_1)连接按钮。

sequenceDiagram

participant B as 按钮

participant G as GPIO控制器

participant D as 驱动

B->>G: 按钮按下(电平 0V->3.3V)

G->>D: 触发中断(GIC_SPI,上升沿)

Note over G,D: 响应时间 <10ns

D->>G: 读取状态寄存器,处理事件

D->>G: 清除中断(IC_CLR_INTR)

说明

- 输出时序:GPIO 无固定时钟,驱动通过寄存器直接控制电平。LED 响应为瞬时(<10ns),需串联 330Ω 电阻防止过流。

- 中断时序:中断通过 GIC(Generic Interrupt Controller)处理,需配置 PAD 寄存器(0x32B30000)启用上下拉和中断模式。

- 异常情况:电平不稳定可能导致中断误触发,建议检查上下拉配置(x_reg0 寄存器)。

2.接口表

pl061 接口表

- 表格格式:

| API函数 | 描述 | 参数 | 返回值 |

|---|---|---|---|

| Pl0611::new | 创建gpio实例 | base_addr: Gpio控制器的基地址 | 初始化的gpio控制器 |

| Pl0611::set_func | 设置gpio引脚功能 | self,ch:通道号,func: Gpio功能 | Result<(),IoError>,成功Ok(()), 失败:无效的通道号 |

| Pl0611::int_when | 设置gpio中断条件 | self, ch:通道号,cond:什么时候触发中断,必须先配置为中断模式 | Result<(),IoError> 成功Ok(()), 失败:无效的通道号 |

| Pl0611::set_output | 设置gpio输出值 | self, ch:通道号, val:引脚值 | Result<(),IoError> 成功Ok(()), 失败:无效的通道号(没有配置为输出) |

| Pl0611::get_input | 设置gpio输出值 | self, ch:通道号, | Result<bool,IoError> 成功Ok(value), 失败:无效的通道号 |

飞腾派 GPIO1 接口表

- 表格格式:

| API函数 | 描述 | 参数 | 返回值 |

|---|---|---|---|

| PhytiumGpio::new | 创建gpio实例 | base_addr: Gpio控制器的基地址 | 初始化的gpio控制器 |

| PhytiumGpio::set_func | 设置gpio引脚功能 | self,ch:通道号,func: Gpio功能 | Result<(),IoError>,成功Ok(()), 失败:无效的通道号 |

| PhytiumGpio::set_output | 设置gpio输出值 | self, ch:通道号, val:引脚值 | Result<(),IoError> 成功Ok(()), 失败:无效的通道号(没有配置为输出) |

| PhytiumGpio::get_input | 设置gpio输出值 | self, ch:通道号, | Result<bool,IoError> 成功Ok(value), 失败:无效的通道号 |

-

调用顺序

- 中断模式

- 初始化

- 配置中断模式

- 配置中断条件

- 定义自己的中断函数并注册

- 输入/输出模式

- 初始化

- 配置输入/输出功能

- 输入/输出值

- 中断模式

-

错误处理 IoError::InvChn 不合法的通道

3. 寄存器结构

pl061模块

-

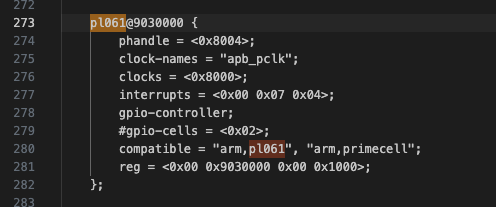

基地址 对于嵌入式平台,device tree是一种常用的方法。这次实现也需要通过设备树的方法获取基地址。不幸的是 qemu 没有直接提供他的设备树,但是启动的时候确实会传递一个默认的设备树。我们通过导出qemu设备树的方法来获取设备树。获得了dts之后,我们在这个dts中搜索 "pl061",可以看到这个:

pl061@9030000说明基地址为 0x9030000。

-

寄存器表

| 寄存器名称 | 偏移 | 寄存器定义 |

|---|---|---|

| GPIODIR | 0x400 | 设置GPIO引脚的输入输出功能,1代表该引脚为输出模式,0代表该引脚为输入模式。 |

| GPIOIS | 0x404 | 中断的触发方式p1,0代表检测电压,1代表检测边缘 |

| GPIOIBE | 0x408 | 中断的触发方式p2,0代表中断通过GPIOIEV来控制,1代表上升沿和下降沿都能触发中断 |

| GPIOIEV | 0x40c | 中断的触发方式设置p3,如果中断设置为边沿触发,0代表设置为下降沿触发,1代表上升沿触发;如果中断设置为电平触发, 0代表低电平,1代表高电平 |

| GPIOIE | 0x410 | 1是使能中断,0是去使能中断 |

飞腾派GPIO1模块

-

基地址 通过数据手册可以查出,GPIO1模块的基地址为0x000_2803_5000。

-

寄存器表

| 寄存器名称 | 偏移 | 寄存器定义 |

|---|---|---|

| GPIO_SWPORT_DR | 0x00 | 每一bit定义了对应引脚的输出值(当配置为输出模式时)。如果该引脚被配置为输出模式,写入这个寄存器的值将会被输出。1对应高电平,0对应低电平。 |

| GPIO_SWPORT_DDR | 0x04 | 每一bit定义了对应引脚的in/out属性。1代表该引脚为输出模式,0代表该引脚为输入模式。 |

| GPIO_EXT_PORT | 0x08 | 每一bit定义了对应引脚的引脚值。1代表对应引脚输出为高,0代表输出为低。 |

4 具体实现讲解

qemu平台关机实验

对于一些简单的设备,qemu能够很好的进行模拟。因此,对于部分没有开发板而想尝试进行驱动开发学习的同学,我们提供了基于qemu的部分实验。

-

在arceos代码仓库下,使用example为helloworld,先尝试运行得到以下结果。

运行结果

arceos git:(main)✗ make A=examples/helloworld PLATFORM=aarch64-qemu-virt ARCH=aarch64 LOG=debug FEATURES="driver-ramdisk,irq" run ACCEL=n GRAPHIC=n... # skip part build log axconfig-gen configs/defconfig.toml configs/platforms/aarch64-qemu-virt.toml -w smp=1 -w arch=aarch64 -w platform=aarch64-qemu-virt -o "/Users/jp/code/arceos/.axconfig.toml" -c "/Users/jp/code/arceos/.axconfig.toml" Building App: helloworld, Arch: aarch64, Platform: aarch64-qemu-virt, App type: rust cargo -C examples/helloworld build -Z unstable-options --target aarch64-unknown-none-softfloat --target-dir /Users/jp/code/arceos/target --release --features "axstd/log-level-debug axstd/driver-ramdisk axstd/irq" Finished `release` profile [optimized] target(s) in 0.08s rust-objcopy --binary-architecture=aarch64 examples/helloworld/helloworld_aarch64-qemu-virt.elf --strip-all -O binary examples/helloworld/helloworld_aarch64-qemu-virt.bin Running on qemu... qemu-system-aarch64 -m 128M -smp 1 -cpu cortex-a72 -machine virt -kernel examples/helloworld/helloworld_aarch64-qemu-virt.bin -nographic d8888 .d88888b. .d8888b. d88888 d88P" "Y88b d88P Y88b d88P888 888 888 Y88b. d88P 888 888d888 .d8888b .d88b. 888 888 "Y888b. d88P 888 888P" d88P" d8P Y8b 888 888 "Y88b. d88P 888 888 888 88888888 888 888 "888 d8888888888 888 Y88b. Y8b. Y88b. .d88P Y88b d88P d88P 888 888 "Y8888P "Y8888 "Y88888P" "Y8888P" arch = aarch64 platform = aarch64-qemu-virt target = aarch64-unknown-none-softfloat build_mode = release log_level = debug smp = 1 [ 0.001902 0 axruntime:130] Logging is enabled. [ 0.002488 0 axruntime:131] Primary CPU 0 started, dtb = 0x44000000. [ 0.002738 0 axruntime:133] Found physcial memory regions: [ 0.002968 0 axruntime:135] [PA:0x40200000, PA:0x40206000) .text (READ | EXECUTE | RESERVED) [ 0.003304 0 axruntime:135] [PA:0x40206000, PA:0x40209000) .rodata (READ | RESERVED) [ 0.003502 0 axruntime:135] [PA:0x40209000, PA:0x4020d000) .data .tdata .tbss .percpu (READ | WRITE | RESERVED) [ 0.003714 0 axruntime:135] [PA:0x4020d000, PA:0x4024d000) boot stack (READ | WRITE | RESERVED) [ 0.003892 0 axruntime:135] [PA:0x4024d000, PA:0x40250000) .bss (READ | WRITE | RESERVED) [ 0.004080 0 axruntime:135] [PA:0x40250000, PA:0x48000000) free memory (READ | WRITE | FREE) [ 0.004290 0 axruntime:135] [PA:0x9000000, PA:0x9001000) mmio (READ | WRITE | DEVICE | RESERVED) [ 0.004482 0 axruntime:135] [PA:0x9100000, PA:0x9101000) mmio (READ | WRITE | DEVICE | RESERVED) [ 0.004662 0 axruntime:135] [PA:0x8000000, PA:0x8020000) mmio (READ | WRITE | DEVICE | RESERVED) [ 0.004806 0 axruntime:135] [PA:0xa000000, PA:0xa004000) mmio (READ | WRITE | DEVICE | RESERVED) [ 0.004948 0 axruntime:135] [PA:0x10000000, PA:0x3eff0000) mmio (READ | WRITE | DEVICE | RESERVED) [ 0.005098 0 axruntime:135] [PA:0x4010000000, PA:0x4020000000) mmio (READ | WRITE | DEVICE | RESERVED) [ 0.005284 0 axruntime:150] Initialize platform devices... [ 0.005420 0 axhal::platform::aarch64_common::gic:51] Initialize GICv2... [ 0.006258 0 axruntime:176] Initialize interrupt handlers... [ 0.006466 0 axhal::irq:32] irq=30 enabled [ 0.006830 0 axruntime:188] Primary CPU 0 init OK. Hello, world! [ 0.007086 0 axruntime:201] main task exited: exit_code=0 [ 0.007248 0 axhal::platform::aarch64_common::psci:98] Shutting down... -

由于目前arceos是unikernel模式,特权级为el1,所以可以直接在 main.c 中操作设备地址(需要注意的是,这不是一种正确的做法。但对于初学者,为了不在一开始就去研究arecos的复杂代码框架,可以短暂的把实现代码写在这儿。),将pl061模块的三号引脚配置为irq模式。

#![allow(unused)] fn main() { // examples/helloworld/main.c ... /// 0x9030000 是 qemu模拟的aarch64-qemu-virt机器的 pl061模块的基地址(物理地址)。 /// irq number 39 从 aarch64-qemu-virt机器的设备树中找到,7 + 外部中断base(32) = 39 unsafe fn set_gpio_irq_enable() { // PHYS_VIRT_OFFSET 是 arceos 初始化时,将物理内存映射时进行的偏移。 let base_addr = (0x9030000 + PHYS_VIRT_OFFSET) as *mut u8; // pl061的3号引脚 let pin = 3; // 将interrupt设置为边缘触发 let gpio_is = base_addr.add(0x404); *gpio_is = *gpio_is & !(1 << pin); // 设置触发事件 let gpio_iev = base_addr.add(0x40c); *gpio_iev = *gpio_iev & !(1 << pin); // 设置中断使能 let gpio_ie = base_addr.add(0x410); *gpio_ie = 0; *gpio_ie = *gpio_ie | (1 << pin); fn shut_down() { println!("shutdown function called"); unsafe { let base_addr = (0x9030000 + PHYS_VIRT_OFFSET) as *mut u8; let pin = 3; // clear interrupt let gpio_ic = base_addr.add(0x41c); *gpio_ic = (1 << pin); // 关机命令 core::arch::asm!( "mov w0, #0x18; hlt #0xf000" ) } }; register_handler(39, shut_down); println!("set irq done"); } } -

并将中断号注册到 GIC(generic interrupt controller)中,中断号是39。

#![allow(unused)] fn main() { // examples/helloworld/main.c ... /// 0x9030000 是 qemu模拟的aarch64-qemu-virt机器的 pl061模块的基地址(物理地址)。 /// irq number 39 从 aarch64-qemu-virt机器的设备树中找到,7 + 外部中断base(32) = 39 unsafe fn set_gpio_irq_enable() { // PHYS_VIRT_OFFSET 是 arceos 初始化时,将物理内存映射时进行的偏移。 let base_addr = (0x9030000 + PHYS_VIRT_OFFSET) as *mut u8; // pl061的3号引脚 let pin = 3; // 将interrupt设置为边缘触发 let gpio_is = base_addr.add(0x404); *gpio_is = *gpio_is & !(1 << pin); // 设置触发事件 let gpio_iev = base_addr.add(0x40c); *gpio_iev = *gpio_iev & !(1 << pin); // 设置中断使能 let gpio_ie = base_addr.add(0x410); *gpio_ie = 0; *gpio_ie = *gpio_ie | (1 << pin); fn shut_down() { println!("shutdown function called"); unsafe { let base_addr = (0x9030000 + PHYS_VIRT_OFFSET) as *mut u8; let pin = 3; // clear interrupt let gpio_ic = base_addr.add(0x41c); *gpio_ic = (1 << pin); // 关机命令,可以用别的函数替代 core::arch::asm!( "mov w0, #0x18; hlt #0xf000" ) } }; // register handler 会同时将注册和在gic中使能中断完成。 register_handler(39, shut_down); println!("set irq done"); } } -

在main中死循环,等待gpio触发中断。

#[cfg_attr(feature = "axstd", unsafe(no_mangle))] fn main() { println!("Hello, world!"); unsafe { set_gpio_irq_enable(); } println!("loop started!"); loop { sleep(time::Duration::from_millis(10)); } } -

重新执行第一步命令,若无报错,输入

ctrl + a + c进入qemu的console模式,输入system_powerdown时,qemu会模拟一次中断。... [ 0.005842 0 axhal::platform::aarch64_common::gic:51] Initialize GICv2... [ 0.006358 0 axruntime:176] Initialize interrupt handlers... [ 0.006554 0 axhal::irq:32] irq=30 enabled [ 0.007232 0 axruntime:188] Primary CPU 0 init OK. Hello, world! GPIORIS=0x0 [ 0.007688 0 axhal::irq:32] irq=39 enabled set irq done loop started! QEMU 9.2.0 monitor - type 'help' for more information (qemu) syst system_powerdown system_reset system_wakeup (qemu) system_powerdown -

GIC 会将中断分发给 arm 某个核心(由于我们是单核,不存在分发), cpu对我们注册的关机函数进行回调。

... (qemu) system_powerdown (qemu) shutdown function called [ 50.194414 0 axruntime::lang_items:5] panicked at /Users/jp/.cargo/registry/src/mirrors.ustc.edu.cn-38d0e5eb5da2abae/axcpu-0.1.0/src/aarch64/trap.rs:112:13: Unhandled synchronous exception @ 0xffff0000402010b0: ESR=0x2000000 (EC 0b000000, ISS 0x0) [ 50.195002 0 axhal::platform::aarch64_common::psci:98] Shutting down...

飞腾派点灯实验

基本思想是将GPIO配置为作为输出模式,对应的,这个GPIO可以输出为高电平或者低电平。我们都学过初中物理,知道当一个led灯两侧有足够的电压和电流的时候,它就会亮。不过一般的GPIO线输出电流能力都不强,不足以驱动一个led灯。所以一般会用以下两种方式来实现:

- led正极接电源,负极接gpio。gpio输出为低时,led点亮。

- led接 mos 管的gate。一般来说,GPIO为高电压时,会使得mos管闭合,led点亮;反之则熄灭。

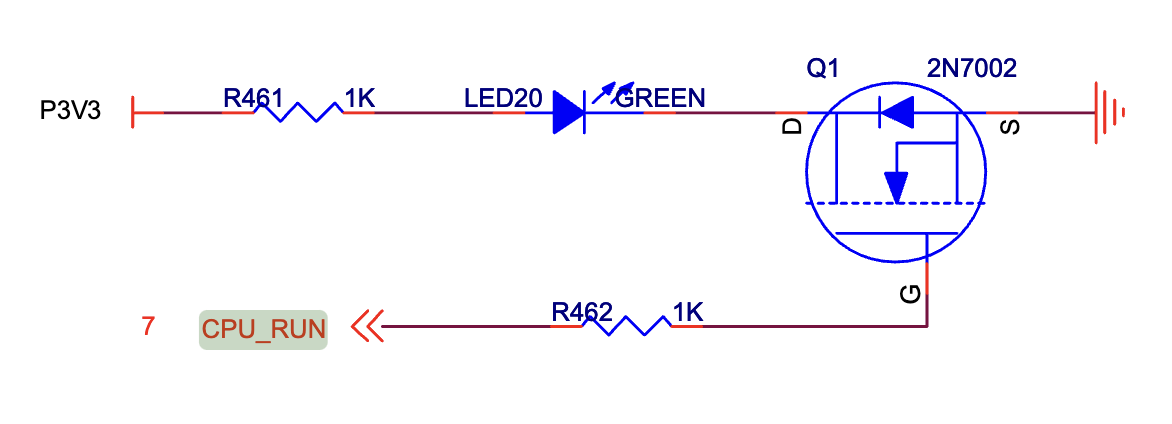

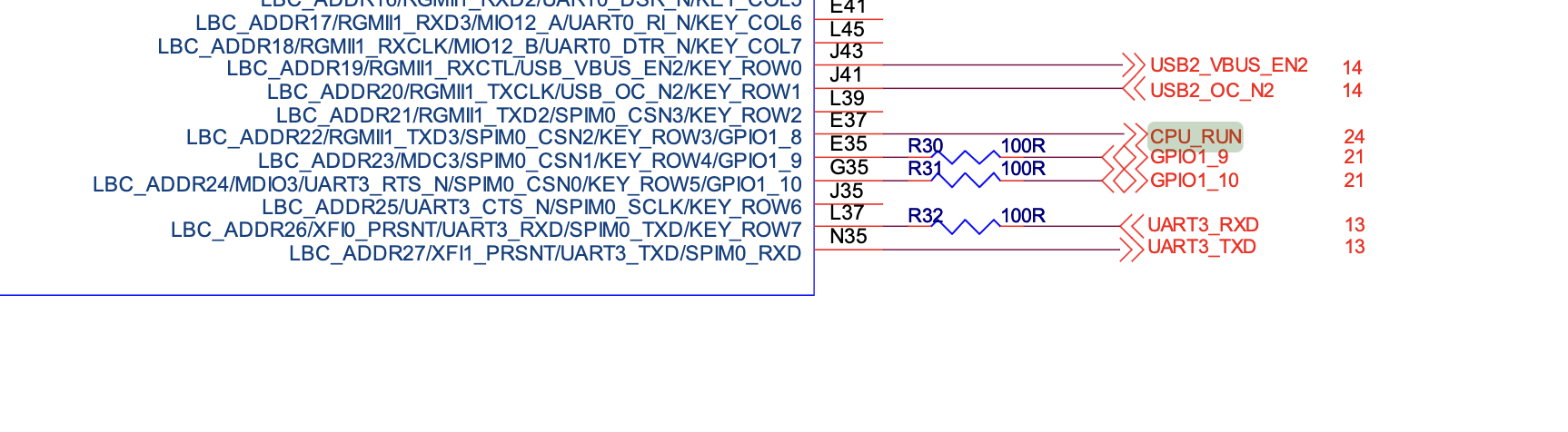

参照飞腾派的硬件原理图,板子上有一个灯可以被我们控制,也就是led20,控制方法为第二种方法,控制GPIO线为GPIO1_8。

当然,如果你愿意,飞腾派开发板提供了很多GPIO的拓展线。你可以自己实现一套电路来点亮外接的led灯。

我们最终要实现led灯的"心跳"效果,即 亮1秒,暗1秒,如此往复循环。

- 编写驱动代码,实现 set_dir 和 set_data 操作,示例代码如下:

#![allow(unused)] fn main() { use bitflags::bitflags; use safe_mmio::fields::ReadWrite; use zerocopy::{FromBytes, Immutable, IntoBytes, KnownLayout}; #[derive(Clone, Eq, FromBytes, Immutable, IntoBytes, KnownLayout, PartialEq)] #[repr(C, align(4))] pub struct PhitiumGpio { data: ReadWrite<GpioPins>, resv: ReadWrite<u16>, dir: ReadWrite<GpioPins>, resv2: ReadWrite<u16>, } #[repr(transparent)] #[derive(Copy, Clone, Debug, Eq, FromBytes, Immutable, IntoBytes, KnownLayout, PartialEq)] pub struct GpioPins(u16); bitflags! { impl GpioPins: u16 { const p0 = 1<<0; const p1 = 1<<1; const p2 = 1<<2; const p3 = 1<<3; const p4 = 1<<4; const p5 = 1<<5; const p6 = 1<<6; const p7 = 1<<7; const p8 = 1<<8; const p9 = 1<<9; const p10 = 1<<10; const p11 = 1<<11; const p12 = 1<<12; const p13 = 1<<13; const p14 = 1<<14; const p15 = 1<<15; } } impl PhitiumGpio { pub fn new(base: usize) -> &'static mut Self { let b = base as *mut PhitiumGpio; unsafe { &mut (*b) } } pub fn set_pin_dir(&mut self, pin: GpioPins, dir: bool) { let mut status = self.dir.0.bits(); debug!("dir data = {status}"); let pb = pin.bits(); if dir == true { status |= pb; } else { status &= !pb; } debug!("dir data = {status}"); self.dir.0 = (GpioPins::from_bits_truncate(status)); } pub fn set_pin_data(&mut self, pin: GpioPins, data: bool) { let mut status = self.dir.0.bits(); debug!(" data = {status}"); let pb = pin.bits(); if data == true { status |= pb; } else { status &= !pb; } debug!(" data = {status}"); self.data.0 = (GpioPins::from_bits_truncate(status)); } } pub use crate::mem::phys_to_virt; pub use memory_addr::PhysAddr; pub const BASE1: PhysAddr = pa!(0x28035000); } - 由于我们目前暂时没有文件系统,无法通过读写文件的方式来控制GPIO。这里直接在main.rs中实例一个GPIO控制器进行相关初始化。

// examples/helloworld/src/main.rs #![cfg_attr(feature = "axstd", no_std)] #![cfg_attr(feature = "axstd", no_main)] use core::time; #[cfg(feature = "axstd")] use axstd::println; use axstd::thread::sleep; #[cfg_attr(feature = "axstd", unsafe(no_mangle))] fn main() { println!("Hello, world!"); let gpio0 = axhal::platform::gpio::PhitiumGpio::new( axhal::platform::gpio::phys_to_virt(axhal::platform::gpio::BASE1).into(), ); let p = axhal::platform::gpio::GpioPins::p8; gpio0.set_pin_dir(p, true); let mut data = false; loop { sleep(time::Duration::from_secs(1)); gpio0.set_pin_data(p, data); println!("current data: {data}"); data = !data; } } - 创建一个大loop,在这个loop中,我们不停的将pin 8的值进行反转,反转一次,sleep 1s,这样就实现了1s灭,1s亮的效果。

// examples/helloworld/src/main.rs #![cfg_attr(feature = "axstd", no_std)] #![cfg_attr(feature = "axstd", no_main)] use core::time; #[cfg(feature = "axstd")] use axstd::println; use axstd::thread::sleep; #[cfg_attr(feature = "axstd", unsafe(no_mangle))] fn main() { println!("Hello, world!"); let gpio0 = axhal::platform::gpio::PhitiumGpio::new( axhal::platform::gpio::phys_to_virt(axhal::platform::gpio::BASE1).into(), ); let p = axhal::platform::gpio::GpioPins::p8; gpio0.set_pin_dir(p, true); et mut data = false; loop { sleep(time::Duration::from_secs(1)); gpio0.set_pin_data(p, data); println!("current data: {data}"); data = !data; } }

- 通过

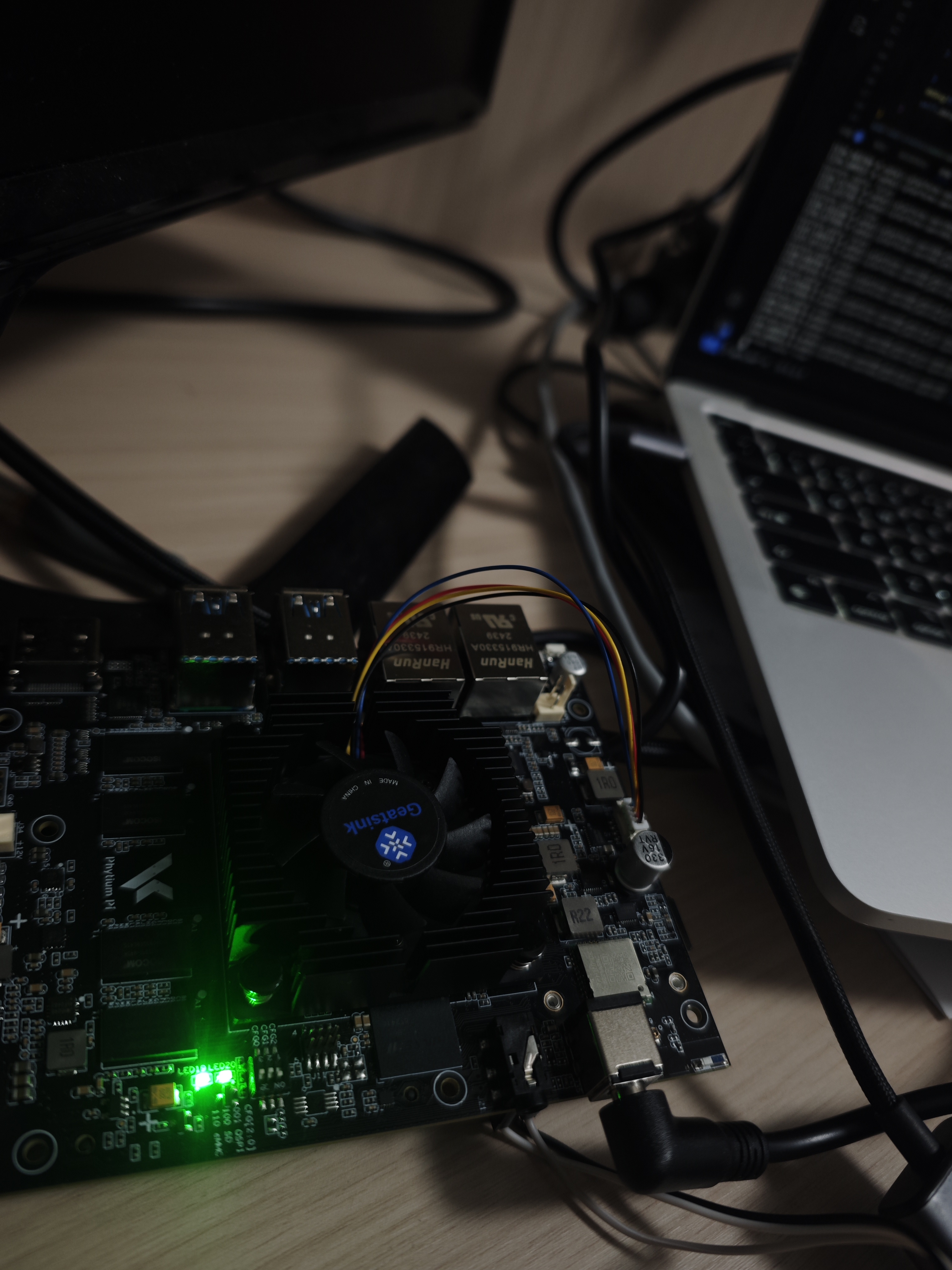

make A=examples/helloworld ARCH=aarch64 PLATFORM=aarch64-phytium-pi FEATURES=irq LOG=debug进行编译,并烧入飞腾派运行。下面是运行日志以及实拍。

运行结果

Starting kernel ...

d8888 .d88888b. .d8888b.

d88888 d88P" "Y88b d88P Y88b

d88P888 888 888 Y88b.

d88P 888 888d888 .d8888b .d88b. 888 888 "Y888b.

d88P 888 888P" d88P" d8P Y8b 888 888 "Y88b.

d88P 888 888 888 88888888 888 888 "888

d8888888888 888 Y88b. Y8b. Y88b. .d88P Y88b d88P

d88P 888 888 "Y8888P "Y8888 "Y88888P" "Y8888P"

arch = aarch64

platform = aarch64-phytium-pi

target = aarch64-unknown-none-softfloat

build_mode = release

log_level = trace

smp = 1

[ 13.461312 0 axruntime:130] Logging is enabled.

[ 13.467040 0 axruntime:131] Primary CPU 0 started, dtb = 0xf9c29000.

[ 13.474591 0 axruntime:133] Found physcial memory regions:

[ 13.481276 0 axruntime:135] [PA:0x90000000, PA:0x90007000) .text (READ | EXECUTE | RESERVED)

[ 13.491083 0 axruntime:135] [PA:0x90007000, PA:0x9000a000) .rodata (READ | RESERVED)

[ 13.500197 0 axruntime:135] [PA:0x9000a000, PA:0x9000e000) .data .tdata .tbss .percpu (READ | WRITE | RESERVED)

[ 13.511655 0 axruntime:135] [PA:0x9000e000, PA:0x9004e000) boot stack (READ | WRITE | RESERVED)

[ 13.521724 0 axruntime:135] [PA:0x9004e000, PA:0x90051000) .bss (READ | WRITE | RESERVED)

[ 13.531272 0 axruntime:135] [PA:0x90051000, PA:0x100000000) free memory (READ | WRITE | FREE)

[ 13.541167 0 axruntime:135] [PA:0x2800c000, PA:0x2800d000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.551496 0 axruntime:135] [PA:0x2800d000, PA:0x2800e000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.561825 0 axruntime:135] [PA:0x2800e000, PA:0x2800f000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.572155 0 axruntime:135] [PA:0x2800f000, PA:0x28010000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.582484 0 axruntime:135] [PA:0x30000000, PA:0x38000000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.592813 0 axruntime:135] [PA:0x40000000, PA:0x50000000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.603142 0 axruntime:135] [PA:0x58000000, PA:0x80000000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.613471 0 axruntime:135] [PA:0x28014000, PA:0x28016000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.623800 0 axruntime:135] [PA:0x28016000, PA:0x28018000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.634130 0 axruntime:135] [PA:0x28018000, PA:0x2801a000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.644459 0 axruntime:135] [PA:0x2801a000, PA:0x2801c000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.654788 0 axruntime:135] [PA:0x2801c000, PA:0x2801e000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.665117 0 axruntime:135] [PA:0x28034000, PA:0x28035000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.675446 0 axruntime:135] [PA:0x28035000, PA:0x28036000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.685776 0 axruntime:135] [PA:0x28036000, PA:0x28037000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.696105 0 axruntime:135] [PA:0x28037000, PA:0x28038000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.706434 0 axruntime:135] [PA:0x28038000, PA:0x28039000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.716763 0 axruntime:135] [PA:0x28039000, PA:0x2803a000) mmio (READ | WRITE | DEVICE | RESERVED)

[ 13.727093 0 axruntime:150] Initialize platform devices...

[ 13.733776 0 axhal::platform::aarch64_common::gic:51] Initialize GICv2...

[ 13.741897 0 axhal::platform::aarch64_common::gic:27] GICD set enable: 30 true

[ 13.750182 0 axhal::platform::aarch64_common::gic:27] GICD set enable: 116 true

[ 13.758688 0 axruntime:176] Initialize interrupt handlers...

[ 13.765545 0 axhal::platform::aarch64_common::gic:36] register handler irq 30

[ 13.773878 0 axhal::platform::aarch64_common::gic:27] GICD set enable: 30 true

[ 13.782298 0 axruntime:188] Primary CPU 0 init OK.

Hello, world!

[ 13.789589 0 axhal::platform::aarch64_phytium_pi::gpio:46] dir data = 0

[ 13.797401 0 axhal::platform::aarch64_phytium_pi::gpio:53] dir data = 256

[ 14.805386 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 14.810239 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 0

current data: false

[ 15.819614 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 15.824467 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 256

current data: true

[ 16.833928 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 16.838781 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 0

current data: false

[ 17.848156 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 17.853009 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 256

current data: true

[ 18.862470 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 18.867323 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 0

current data: false

[ 19.876698 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 19.881551 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 256

current data: true

[ 20.891012 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 20.895865 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 0

current data: false

[ 21.905240 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 21.910093 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 256

current data: true

[ 22.919554 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 22.924407 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 0

current data: false

[ 23.933782 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 23.938635 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 256

current data: true

[ 24.948097 0 axhal::platform::aarch64_phytium_pi::gpio:58] data = 256

[ 24.952950 0 axhal::platform::aarch64_phytium_pi::gpio:65] data = 0

current data: false

5. 开发注意

5.1 优化代码

- 目前驱动代码位于

examples/helloworld/main.c中,这不是一种正确的做法。参考modules/axhal/src/platform/aarch64_common/pl011.rs的实现,在同级目录下实现 pl061.rs。 rust 提供了如tock_registers这样的可以用来定义寄存器的crate,用起来! - 关机函数实际上是触发了一个异常而导致的关机,当把上一步完成后,换成

axhal::misc::terminate来优雅的关机! - 实验2的完整代码在https://github.com/arceos-org/arceos/commit/2e7837a786d13b0a77804d15a10f614ef715150d。

6. 参考资料

pl061_datasheet:

https://github.com/elliott10/dev-hw-driver/blob/main/docs/GPIO-controller-pl061-DDI0190.pdf

导出qemu设备树:

https://blog.51cto.com/u_15072780/3818667

飞腾派硬件原理图:

飞腾派软件开发手册

https://github.com/elliott10/dev-hw-driver/blob/main/phytiumpi/docs/飞腾派软件编程手册V1.0.pdf

7. 测试用例

本次 GPIO 测试的目的:验证 Arceos 的 GPIO 驱动能否正常初始化指定引脚、配置为输出模式,并通过切换高低电平控制调试灯的亮灭,确保驱动的电平控制功能正常。

gpio_test

本测例基于飞腾派的点灯实验,通过观察开发板自带的调试led灯的亮灭来验证gpio的功能。

在开发板上gpio_test命令实现如下:

#![allow(unused)] fn main() { // 在一个循环里,周期性反转引脚的值 fn do_gpio_test(_args: &str) { let mut gpio0 = GPIO0.lock(); let p = gpio::GpioPins::p8; gpio0.set_pin_dir(p, true); for i in 0..10{ sleep(time::Duration::from_millis(1000)); gpio0.set_pin_data(p, data); println!("current data: {data}"); data = !data; } } }

测试过程中,测试机会提示“即将执行 gpio_test 测试命令,请观察调试灯,按 Enter 键开始...”,按下 Enter 后,LED 应交替闪烁(高电平时亮,低电平时灭),周期约 1s。观察到 LED 闪烁后,在测试机终端输入“OK”并回车,测试日志应显示 PASSED。

pytest -vs -m gpio # 观察调试灯是否存在周期性亮灭的现象,输入"OK"则测试通过,否则测试失败

1.2 PWM驱动开发

PWM介绍

PWM(Pulse Width Modulation) 是一种通过调节脉冲宽度(占空比)来模拟不同模拟量输出的数字控制技术。它利用数字信号(高/低电平)控制模拟电路,广泛应用于电机调速、电源转换、LED调光等领域。其核心是通过调整脉冲的“有效时间比例”实现连续可调的电压、功率或信号输出

PWM 最关键的两个参数:频率和占空比。

频率是指单位时间内脉冲信号的周期数。比如开关灯,开关一次算一次周期,在 1s 进行多少次开关(开关一次为一个周期)。

占空比是指一个周期内高电平时间和低电平时间的比例。也拿开关当作例子,总共 100s,开了 50s 灯(高电平),关了 50s 灯(低电平),这时候的占空比就为 50%(比例)。

PWM核心特性

1.占空比可变

- 占空比越大,等效输出电压越高(例:占空比50% ≈ 最大电压的50%)

2.数字模拟转换能力

- 微控制器通过输出高频方波(如10kHz),配合滤波电路,可生成平滑的模拟电压(如0-5V连续可调)

3.控制灵活性强

- 频率可调:适应不同负载需求(电机控制常用6-16kHz,LED调光>80Hz避频闪)

- 动态响应快:占空比可实时调整(如根据传感器反馈调节电机转速)

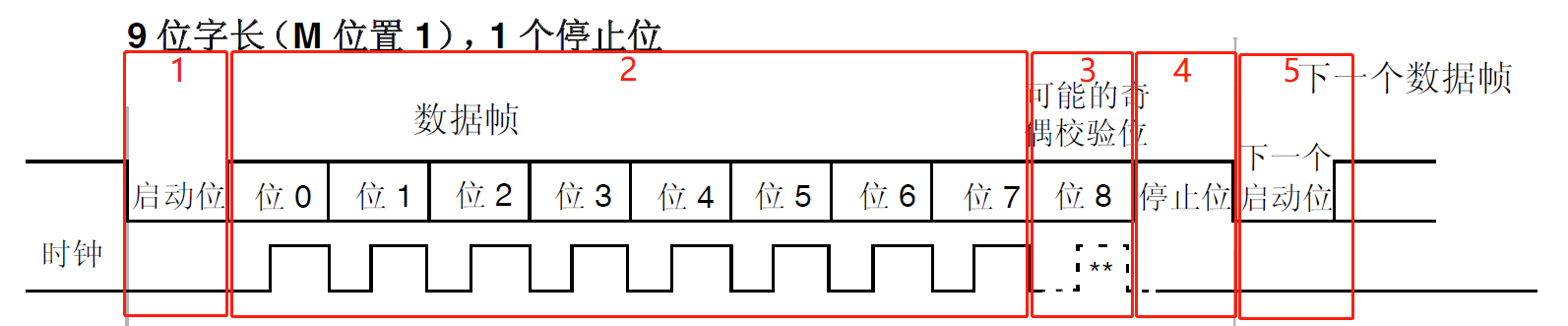

PWM控制原理和工作过程

关键参数

- 周期(T):一个完整脉冲的时间(单位:秒)。

- 频率(f):周期的倒数(f=1/T),决定信号切换速度。

- 脉宽时间(tW):高电平持续时间,直接决定占空比

PWM波形生成过程

1.周期设定

- 通过定时器计数器设定周期值(PWM定时器的工作方式有点像一个精准的节拍器。它的核心是一个计数器,从0开始计数,数到某个设定值(称为模数)后清零,循环往复。这个模数决定了PWM信号的周期)

- 举例:假设模数设为9,计数器会从0数到9,总共10个状态,构成一个完整的周期。

- PWM定时器通常会有个预分频器,用来把主时钟频率降低,方便控制计数器的速度,这里我们假设主时钟频率24 MHz,预分频器可选1、2、4、8、16、32、64、128

- 预分频器的值决定了计数器的时钟频率,计数器的时钟频率 = 主时钟频率 / 预分频器的值

- 当预分频器设为8,计数器的时钟频率为24 MHz / 8 = 3 MHz

2.脉宽调制

- 设置“宽度寄存器”值W控制高电平时间,这里我们还是以上面的例子继续讲解:

- 我们需求电机静止脉宽:1.5毫秒,最大顺时针速度脉宽:1毫秒,最大逆时针速度脉宽:2毫秒

- 脉宽时间tW = W × 0.333微秒,W是宽度寄存器的值,由此

- 电机静止:1.5毫秒 ÷ 0.333微秒 ≈ 4500

- 最大顺时针速度:1毫秒 ÷ 0.333微秒 ≈ 3000

- 最大逆时针速度:2毫秒 ÷ 0.333微秒 ≈ 6000

飞腾派PWM硬件实现

飞腾派集成的 PWM 控制器支持典型的 PWM 功能,有 2 个完全独立的 compare 输出通道。使用 PWM 功能前,需要先配置相关 PAD 复用寄存器,将对应 PAD 配置到对应功能上,即可使用 PWM 功能。

飞腾派PWM硬件模块

| 模块 | 功能 |

|---|---|

| PWM控制器核心模块(处理器内置) | 支持compare输出模式,提供寄存器、FIFO双模式驱动,并支持中断控制:计数器溢出、比较匹配、FIFO空中断 |

| 死区生成器 | 防短路保护,并提供了Bypass(原始信号直通)、FallEdgeOnly(只添加下降沿延迟)、RiseEdgeOnly(只添加上升沿延迟)、FullDeadband(双边延迟)四种工作模式(由DBDLY和DBCTRL控制) |

飞腾派 PWM 设备时序图

飞腾派(Phytium Pi)V3.x 版本的 PWM(脉宽调制)设备通过 PWM 控制器(基址 0x2804_A000~0x2805_1000)生成可调频率和占空比的信号,支持 8 个控制器,每个控制器 2 个通道(PWM0 和 PWM1),输出通过 40-pin 扩展头(如 Pin 32,GPIO1_1)。以下为 PWM 设备的典型时序图,展示通道配置和输出过程,以及中断处理流程(如 FIFO 空中断)。时序图基于 pwm.rs 驱动实现(configure_channel 和 handle_interrupt),参考飞腾派软件编程手册 V1.0(5.24 节),使用 Mermaid 绘制。

PWM 通道配置与输出时序

描述:驱动通过寄存器(tim_ctrl, pwm_period, pwm_ctrl, pwm_ccr)配置 PWM 通道(例如通道 0,频率 1kHz,占空比 50%),启用输出(Pin 32)。过程包括设置分频、周期、占空比和比较模式(ClearOnMatch),最终生成 PWM 波形。

sequenceDiagram

participant D as 驱动

participant P as PWM控制器

participant O as 输出引脚(Pin 32)

D->>P: 写 tim_ctrl(DIV=50000, MODE=Modulo, ENABLE=0)

D->>P: 写 pwm_period(CCR=999) // 1kHz

D->>P: 写 pwm_ctrl(MODE=Compare, CMP=ClearOnMatch, IE=1)

D->>P: 写 pwm_ccr(CCR=500) // 50% 占空比

D->>P: 写 tim_ctrl(ENABLE=1)

P->>O: 输出 PWM 波形(1kHz, 50% 占空比)

Note over P,O: 周期 1ms, 高电平 0.5ms

说明:

- 时序:配置分频(DIV=50000,50MHz/50000=1kHz),周期(CCR=999,1ms),占空比(CCR=500,50%)。启用后(ENABLE=1),PWM 控制器在 10ns 内输出波形。

- 硬件关联:PWM 通道 0(基址 0x2804_A000,偏移 0x400~0x414),输出至 Pin 32(需 PAD 配置为 PWM,x_reg0=4)。

- 约束:频率切换需等待计数器归零(<1ms),确保外设空闲(如 UART 无传输)。

PWM 中断处理时序(FIFO 模式)

描述:驱动启用 FIFO 模式(DUTY_SEL=FIFO),配置通道 0(1kHz,50% 占空比),处理 FIFO 空中断(STATE::FIFO_EMPTY)。当计数器归零(tim_cnt=0),驱动重新填充占空比值,保持连续输出。

sequenceDiagram

participant D as 驱动

participant P as PWM控制器

participant G as GIC中断控制器

D->>P: 写 pwm_ctrl(FIFO_EMPTY_ENABLE=1, DUTY_SEL=FIFO)

D->>P: 填充 pwm_ccr(CCR=500, 4次) // 50% 占空比

P->>G: 触发 FIFO 空中断(STATE::FIFO_EMPTY=1)

G->>D: 中断信号(GIC SPI)

D->>P: 检查 tim_cnt(CNT=0)

D->>P: 填充 pwm_ccr(CCR=500)

D->>P: 清除 STATE::FIFO_EMPTY(写1)

Note over P,D: 中断响应 <10ns

说明:

- 时序:FIFO 空时触发中断(<10ns),驱动检查计数器(CNT=0),填充占空比(CCR=500),清除中断标志(RW1C)。中断周期与 PWM 频率一致(1ms for 1kHz)。

- 硬件关联:中断通过 GIC(基址 0xFF84_1000),需 pinctrl.rs 配置引脚(Pin 32)。状态寄存器(偏移 0x408/0x808)使用 RW1C 清除。

- 约束:FIFO 需预填充 4 个值,避免空中断频繁触发。

飞腾派PWM驱动API调用表

| API函数 | 描述 | 参数 | 返回值 |

|---|---|---|---|

| PwmDriver::new | 创建 PWM 驱动实例并映射硬件寄存器。 | base_addr: PWM 控制器的物理基地址 | 初始化的 PwmDriver 对象 |

| configure_channel | 配置 PWM 通道参数 | channel: PWM 通道号 (0-7)、config: PwmConfig 结构体,包含:frequency: PWM 频率 (Hz)、duty_cycle: 占空比 (0.0-1.0)、counting_mode: 计数模式 (Modulo/UpAndDown)、deadtime_ns: 死区时间 (纳秒)、use_fifo: 是否使用 FIFO 模式 | Option:成功:Ok(());失败:错误信息(如无效通道、占空比越界等) |

| init_fifo_mode | 初始化 FIFO 模式 | channel: PWM 通道号、 initial_duty: 初始占空比值 | Option:成功:Ok(());失败:错误信息 |

| push_fifo_data | 向 FIFO 推送占空比数据 | channel: PWM 通道号;duty_value: 16 位占空比值 | Option:成功:Ok(());失败:错误信息 |

| enable_channel | 启用 PWM 通道输出 | channel: PWM 通道号 | 无 |

| safe_stop_channel | 安全停止 PWM 输出(防电源瞬变) | channel: PWM 通道号 | 无 |

| enable_multiple_channels | 同时启用多个 PWM 通道 | mask: 通道掩码(bit0=通道0, bit1=通道1, ...) | 无 |

| handle_interrupt | 处理 PWM 中断 | 无 | 无 |

| pwm_init | 初始化 PWM 控制器(高级封装) | base_addr: PWM 控制器物理基地址 | 初始化的 PwmDriver 对象 |

飞腾派 PWM 设备驱动寄存器信息

以下为飞腾派(Phytium Pi)V3.x 版本 PWM(脉宽调制)设备驱动涉及的寄存器信息,基于在 chenlongos/appd 仓库 phytium-pi 分支中实现的 modules/axhal/src/platform/aarch64_phytium_pi/pwm.rs 文件。驱动设计使用 Rust 和 tock_registers 宏,遵循 ArceOS 的 axhal 框架,适配飞腾派 E2000 处理器的 PWM 控制器(支持 8 个控制器,每个控制器 2 个通道)。寄存器信息参考飞腾派软件编程手册 V1.0(表 5-67 和 5.24),包括基地址、寄存器表和位域定义。

基地址

PWM 驱动涉及 8 个 PWM 控制器和全局使能寄存器,基址如下:

| 模块 | 基地址 | 描述 |

|---|---|---|

| PWM 控制器 0 | 0x2804_A000 | PWM0 控制器,2 个通道(PWM0_OUT/PWM1_OUT) |

| PWM 控制器 1 | 0x2804_B000 | PWM1 控制器 |

| PWM 控制器 2 | 0x2804_C000 | PWM2 控制器 |

| PWM 控制器 3 | 0x2804_D000 | PWM3 控制器 |

| PWM 控制器 4 | 0x2804_E000 | PWM4 控制器 |

| PWM 控制器 5 | 0x2804_F000 | PWM5 控制器 |

| PWM 控制器 6 | 0x2805_0000 | PWM6 控制器 |

| PWM 控制器 7 | 0x2805_1000 | PWM7 控制器 |

| 全局使能寄存器 | 0x2807E020 | 控制所有 PWM 控制器的使能(bit 0-7) |

寄存器表

每个 PWM 控制器包含死区控制寄存器(0x0000~0x03FF)和两个通道寄存器(通道 0: 0x0400~0x07FF,通道 1: 0x0800~0x0BFF)。以下为寄存器定义:

| 寄存器名称 | 偏移地址 | 描述 |

|---|---|---|

dbctrl | 0x0000 | 死区控制寄存器,配置死区模式和输出极性。 |

dbdly | 0x0004 | 死区延迟寄存器,设置上升/下降沿延迟周期。 |

ch0_tim_cnt | 0x0400 | 通道 0 当前计数值寄存器,记录定时器计数值。 |

ch0_tim_ctrl | 0x0404 | 通道 0 定时器控制寄存器,配置分频、计数模式和使能。 |

ch0_state | 0x0408 | 通道 0 状态寄存器,记录中断状态(FIFO 满/空、溢出、比较匹配)。 |

ch0_pwm_period | 0x040C | 通道 0 周期寄存器,设置 PWM 周期值。 |

ch0_pwm_ctrl | 0x0410 | 通道 0 PWM 控制寄存器,配置输出模式、FIFO 和中断。 |

ch0_pwm_ccr | 0x0414 | 通道 0 占空比寄存器,设置比较值(占空比)。 |

ch1_tim_cnt | 0x0800 | 通道 1 当前计数值寄存器,记录定时器计数值。 |

ch1_tim_ctrl | 0x0804 | 通道 1 定时器控制寄存器,配置分频、计数模式和使能。 |

ch1_state | 0x0808 | 通道 1 状态寄存器,记录中断状态。 |

ch1_pwm_period | 0x080C | 通道 1 周期寄存器,设置 PWM 周期值。 |

ch1_pwm_ctrl | 0x0810 | 通道 1 PWM 控制寄存器,配置输出模式、FIFO 和中断。 |

ch1_pwm_ccr | 0x0814 | 通道 1 占空比寄存器,设置比较值(占空比)。 |

寄存器位域设置

以下详细描述每个寄存器的位域,包括用途、有效值和默认状态。

dbctrl (偏移 0x0000, 读写)

- OUT_MODE (bit 4-5, 2 bits)

- 用途:配置死区输出模式。

- 有效值:

- 0b00 = Bypass(无死区)

- 0b01 = FallEdgeOnly(仅下降沿)

- 0b10 = RiseEdgeOnly(仅上升沿)

- 0b11 = FullDeadband(双边死区)

- 默认值:0b00

- 描述:控制 PWM0_OUT 和 PWM1_OUT 的死区行为(如电机驱动)。

- POLSEL (bit 2-3, 2 bits)

- 用途:配置输出极性。

- 有效值:

- 0b00 = AH(PWM0_OUT/PWM1_OUT 不翻转)

- 0b01 = ALC(PWM0_OUT 翻转)

- 0b10 = AHC(PWM1_OUT 翻转)

- 0b11 = AL(两者翻转)

- 默认值:0b00

- 描述:调整输出信号极性。

- IN_MODE (bit 1, 1 bit)

- 用途:选择死区输入源。

- 有效值:0 = PWM0,1 = PWM1

- 默认值:0

- 描述:选择 PWM 通道作为死区输入。

- DB_SW_RST (bit 0, 1 bit)

- 用途:软件复位死区控制。

- 有效值:0 = 正常,1 = 复位

- 默认值:0

- 描述:复位死区模块。

dbdly (偏移 0x0004, 读写)

- DBFED (bit 10-19, 10 bits)

- 用途:下降沿死区延迟周期(0~1023)。

- 默认值:0

- 描述:设置下降沿延迟(ns 级,基于 50MHz 时钟)。

- DBRED (bit 0-9, 10 bits)

- 用途:上升沿死区延迟周期(0~1023)。

- 默认值:0

- 描述:设置上升沿延迟。

ch0_tim_cnt / ch1_tim_cnt (偏移 0x0400/0x0800, 读写)

- CNT (bit 0-15, 16 bits)

- 用途:当前计数值。

- 默认值:0

- 描述:记录 PWM 计数器状态,用于中断或轮询。

ch0_tim_ctrl / ch1_tim_ctrl (偏移 0x0404/0x0804, 读写)

- DIV (bit 16-27, 12 bits)

- 用途:分频系数(1~4095)。

- 默认值:0

- 描述:基于 50MHz 系统时钟,计算频率(freq = 50MHz / DIV)。

- GIE (bit 5, 1 bit)

- 用途:全局中断使能。

- 有效值:0 = 禁用,1 = 启用

- 默认值:0

- 描述:控制所有中断输出。

- OVFIF_ENABLE (bit 4, 1 bit)

- 用途:溢出中断使能。

- 有效值:0 = 禁用,1 = 启用

- 默认值:0

- 描述:启用计数器溢出中断。

- MODE (bit 2, 1 bit)

- 用途:计数模式。

- 有效值:0 = Modulo(模计数),1 = UpAndDown(三角计数)

- 默认值:0

- 描述:控制计数行为。

- ENABLE (bit 1, 1 bit)

- 用途:通道使能。

- 有效值:0 = 禁用,1 = 启用

- 默认值:0

- 描述:启动 PWM 输出。

- SW_RST (bit 0, 1 bit)

- 用途:软件复位通道。

- 有效值:0 = 正常,1 = 复位

- 默认值:0

- 描述:复位计数器。

ch0_state / ch1_state (偏移 0x0408/0x0808, 读写)

- FIFO_FULL (bit 3, 1 bit, RW1C)

- 用途:FIFO 满中断标志,写 1 清除。

- 默认值:0

- 描述:指示 FIFO 满状态。

- FIFO_EMPTY (bit 2, 1 bit, RW1C)

- 用途:FIFO 空中断标志,写 1 清除。

- 默认值:0

- 描述:触发 FIFO 数据填充。

- OVFIF (bit 1, 1 bit, RW1C)

- 用途:计数器溢出中断标志,写 1 清除。

- 默认值:0

- 描述:指示周期完成。

- CHIF (bit 0, 1 bit, RW1C)

- 用途:比较匹配中断标志,写 1 清除。

- 默认值:0

- 描述:指示占空比匹配。

ch0_pwm_period / ch1_pwm_period (偏移 0x040C/0x080C, 读写)

- CCR (bit 0-15, 16 bits)

- 用途:周期值(实际周期 = CCR + 1)。

- 默认值:0

- 描述:设置 PWM 周期(如 999 for 1kHz)。

ch0_pwm_ctrl / ch1_pwm_ctrl (偏移 0x0410/0x0810, 读写)

- FIFO_EMPTY_ENABLE (bit 9, 1 bit)

- 用途:FIFO 空中断使能。

- 有效值:0 = 禁用,1 = 启用

- 默认值:0

- 描述:控制 FIFO 空中断。

- DUTY_SEL (bit 8, 1 bit)

- 用途:占空比模式。

- 有效值:0 = Register,1 = FIFO

- 默认值:0

- 描述:选择占空比数据源。

- ICOV (bit 7, 1 bit)

- 用途:初始输出值。

- 有效值:0 = 低,1 = 高

- 默认值:0

- 描述:设置 PWM 初始电平。

- CMP (bit 4-6, 3 bits)

- 用途:比较输出行为。

- 有效值:

- 0b000 = SetOnMatch

- 0b001 = ClearOnMatch

- 0b010 = ToggleOnMatch

- 0b011 = SetOnUpClearOnDown

- 0b100 = ClearOnUpSetOnDown

- 0b101 = ClearOnCCRSetOnPeriod

- 0b110 = SetOnCCRClearOnPeriod

- 0b111 = Initialize

- 默认值:0b000

- 描述:控制 PWM 输出动作。

- IE (bit 3, 1 bit)

- 用途:比较中断使能。

- 有效值:0 = 禁用,1 = 启用

- 默认值:0

- 描述:控制匹配中断。

- MODE (bit 2, 1 bit)

- 用途:PWM 模式。

- 有效值:0 = FreeRunning,1 = Compare

- 默认值:0

- 描述:选择运行或比较模式。

ch0_pwm_ccr / ch1_pwm_ccr (偏移 0x0414/0x0814, 读写)

- CCR (bit 0-15, 16 bits)

- 用途:占空比值。

- 默认值:0

- 描述:设置 PWM 占空比(如 500 for 50%)。

飞腾派 PWM 驱动实现讲解

寄存器定义部分

#![allow(unused)] fn main() { register_structs! { pub PwmRegisters { (0x0000 => dbctrl: ReadWrite<u32, DBCTRL::Register>), (0x0004 => dbdly: ReadWrite<u32, DBDLY::Register>), (0x0008 => _reserved_db: [u8; 0x3F8]), (0x0400 => ch0_tim_cnt: ReadWrite<u32, TIM_CNT::Register>), (0x0404 => ch0_tim_ctrl: ReadWrite<u32, TIM_CTRL::Register>), (0x0408 => ch0_state: ReadWrite<u32, STATE::Register>), (0x040C => ch0_pwm_period: ReadWrite<u32, PWM_PERIOD::Register>), (0x0410 => ch0_pwm_ctrl: ReadWrite<u32, PWM_CTRL::Register>), (0x0414 => ch0_pwm_ccr: ReadWrite<u32, PWM_CCR::Register>), (0x0418 => _reserved_ch0: [u8; 0x3E8]), (0x0800 => ch1_tim_cnt: ReadWrite<u32, TIM_CNT::Register>), (0x0804 => ch1_tim_ctrl: ReadWrite<u32, TIM_CTRL::Register>), (0x0808 => ch1_state: ReadWrite<u32, STATE::Register>), (0x080C => ch1_pwm_period: ReadWrite<u32, PWM_PERIOD::Register>), (0x0810 => ch1_pwm_ctrl: ReadWrite<u32, PWM_CTRL::Register>), (0x0814 => ch1_pwm_ccr: ReadWrite<u32, PWM_CCR::Register>), (0x0818 => @END), } } }

**讲解:**使用 tock_registers 宏定义 PWM 寄存器布局,每个控制器分为死区控制(0x0000~0x03FF)和通道寄存器(ch0: 0x0400~0x07FF, ch1: 0x0800~0x0BFF)。死区寄存器包括 dbctrl(死区模式/极性,0x0)和 dbdly(延迟周期,0x4)。每个通道有 tim_cnt(当前计数值,0x400/0x800)、tim_ctrl(分频/模式,0x404/0x804)、state(中断状态,0x408/0x808)、pwm_period(周期,0x40C/0x80C)、pwm_ctrl(输出行为,0x410/0x810)、pwm_ccr(占空比,0x414/0x814)。宏生成 ReadWrite 接口,确保类型安全。

位域定义部分

#![allow(unused)] fn main() { register_bitfields! { u32, DBCTRL [ OUT_MODE OFFSET(4) NUMBITS(2) [Bypass = 0b00, FallEdgeOnly = 0b01, RiseEdgeOnly = 0b10, FullDeadband = 0b11], POLSEL OFFSET(2) NUMBITS(2) [AH = 0b00, ALC = 0b01, AHC = 0b10, AL = 0b11], IN_MODE OFFSET(1) NUMBITS(1) [PWM0 = 0, PWM1 = 1], DB_SW_RST OFFSET(0) NUMBITS(1) [Normal = 0, ResetActive = 1] ], DBDLY [ DBFED OFFSET(10) NUMBITS(10) [], DBRED OFFSET(0) NUMBITS(10) [] ], TIM_CNT [CNT OFFSET(0) NUMBITS(16) []], TIM_CTRL [ DIV OFFSET(16) NUMBITS(12) [], GIE OFFSET(5) NUMBITS(1) [], OVFIF_ENABLE OFFSET(4) NUMBITS(1) [], MODE OFFSET(2) NUMBITS(1) [Modulo = 0, UpAndDown = 1], ENABLE OFFSET(1) NUMBITS(1) [Disabled = 0, Enabled = 1], SW_RST OFFSET(0) NUMBITS(1) [Normal = 0, ResetActive = 1] ], STATE [ FIFO_FULL OFFSET(3) NUMBITS(1) [], FIFO_EMPTY OFFSET(2) NUMBITS(1) [], OVFIF OFFSET(1) NUMBITS(1) [], CHIF OFFSET(0) NUMBITS(1) [] ], PWM_PERIOD [CCR OFFSET(0) NUMBITS(16) []], PWM_CTRL [ FIFO_EMPTY_ENABLE OFFSET(9) NUMBITS(1) [], DUTY_SEL OFFSET(8) NUMBITS(1) [Register = 0, FIFO = 1], ICOV OFFSET(7) NUMBITS(1) [], CMP OFFSET(4) NUMBITS(3) [SetOnMatch = 0b000, ClearOnMatch = 0b001, ToggleOnMatch = 0b010, SetOnUpClearOnDown = 0b011, ClearOnUpSetOnDown = 0b100, ClearOnCCRSetOnPeriod = 0b101, SetOnCCRClearOnPeriod = 0b110, Initialize = 0b111], IE OFFSET(3) NUMBITS(1) [], MODE OFFSET(2) NUMBITS(1) [FreeRunning = 0, Compare = 1] ], PWM_CCR [CCR OFFSET(0) NUMBITS(16) []] } }

**讲解:**PwmConfig 定义通道配置(频率、占空比、计数模式等)。PwmChannel 存储通道状态(config 和 enabled)。PwmController 管理 2 个通道(base 地址如 0x2804_A000)。PwmSystem 包含 8 个控制器(基址 0x2804_A000~0x2805_1000)。全局使能寄存器(0x2807E020)控制所有控制器。SYSTEM_CLK=50MHz 匹配 clock.rs,CHANNELS_PER_CONTROLLER=2 符合手册。

函数分析:PwmController 方法

#![allow(unused)] fn main() { impl PwmController { pub unsafe fn new(base_addr: usize) -> Self { Self { base: base_addr, channels: [ PwmChannel { config: None, enabled: false }, PwmChannel { config: None, enabled: false } ], } } fn registers(&self) -> &PwmRegisters { unsafe { &*(self.base as *const PwmRegisters) } } } }

讲解:

- new:初始化控制器,设置基址(e.g., 0x2804_A000),初始化 2 个通道(未配置,未启用)。unsafe 处理指针。

- registers:返回寄存器视图,unsafe 确保基址有效。

函数分析:configure_channel()

#![allow(unused)] fn main() { pub fn configure_channel(&mut self, channel: usize, config: PwmConfig) -> Result<(), &'static str> { if channel >= CHANNELS_PER_CONTROLLER { return Err("Invalid channel number"); } if config.duty_cycle > 1.0 || config.duty_cycle < 0.0 { return Err("Duty cycle must be between 0.0 and 1.0"); } self.disable_channel(channel); let div = (SYSTEM_CLK / config.frequency) as u16; let period_cycles = (SYSTEM_CLK as f32 / (div as f32 * config.frequency as f32)) as u32; let period_reg = period_cycles.checked_sub(1).ok_or("Period too small")?; if period_reg > 0xFFFF { return Err("Period value too large"); } let duty_cycles = (period_reg as f32 * config.duty_cycle) as u16; let regs = self.registers(); if let Some(deadtime) = config.deadtime_ns { let delay_cycles = (deadtime as f32 * SYSTEM_CLK as f32 / 1e9) as u16; let delay_cycles = delay_cycles.min((1 << 10) - 1); regs.dbdly.write(DBDLY::DBRED.val(delay_cycles) + DBDLY::DBFED.val(delay_cycles)); regs.dbctrl.modify(DBCTRL::OUT_MODE::FullDeadband + DBCTRL::IN_MODE::PWM0 + DBCTRL::POLSEL::AH); } let ch_reg = self.get_channel_reg(channel); ch_reg.tim_ctrl.write(TIM_CTRL::DIV.val(div.into()) + TIM_CTRL::MODE.val(config.counting_mode) + TIM_CTRL::ENABLE::Disabled); ch_reg.pwm_period.write(PWM_PERIOD::CCR.val(period_reg as u16)); ch_reg.pwm_ctrl.modify(PWM_CTRL::MODE::Compare + PWM_CTRL::DUTY_SEL.val(config.use_fifo as u32) + PWM_CTRL::ICOV.val(config.initial_value) + PWM_CTRL::CMP.val(config.output_behavior) + PWM_CTRL::IE::SET); if config.use_fifo { for _ in 0..4 { ch_reg.pwm_ccr.write(PWM_CCR::CCR.val(duty_cycles)); } ch_reg.pwm_ctrl.modify(PWM_CTRL::FIFO_EMPTY_ENABLE::SET); } else { ch_reg.pwm_ccr.write(PWM_CCR::CCR.val(duty_cycles)); } self.channels[channel].config = Some(config); Ok(()) } }

**讲解:**配置 PWM 通道(0 或 1)。检查通道号和占空比(0.0~1.0)。禁用通道,计算分频(div = SYSTEM_CLK / freq)和周期(period_cycles = SYSTEM_CLK / (div * freq))。减 1 写入 pwm_period(手册 5.24.3.6)。计算占空比(duty_cycles = period_reg * duty_cycle)。配置死区(dbctrl/dbdly,100ns 级),设置 tim_ctrl(DIV、MODE)、pwm_ctrl(Compare、DUTY_SEL、ICOV、CMP、IE)、pwm_ccr(占空比)。FIFO 模式预填充 4 个值,启用空中断。保存配置,返回 Ok。

函数分析:enable_channel() / disable_channel() / safe_stop_channel()

#![allow(unused)] fn main() { pub fn enable_channel(&mut self, channel: usize) -> Result<(), &'static str> { if channel >= CHANNELS_PER_CONTROLLER { return Err("Invalid channel number"); } let ch_reg = self.get_channel_reg(channel); ch_reg.tim_ctrl.modify(TIM_CTRL::ENABLE::SET); self.channels[channel].enabled = true; Ok(()) } pub fn disable_channel(&mut self, channel: usize) { let ch_reg = self.get_channel_reg(channel); ch_reg.tim_ctrl.modify(TIM_CTRL::ENABLE::CLEAR); self.channels[channel].enabled = false; } pub fn safe_stop_channel(&mut self, channel: usize) -> Result<(), &'static str> { let ch_reg = self.get_channel_reg(channel); ch_reg.pwm_ccr.write(PWM_CCR::CCR.val(0)); while ch_reg.tim_cnt.read(TIM_CNT::CNT) != 0 { cortex_m::asm::nop(); } self.disable_channel(channel); Ok(()) } }

讲解:

- enable_channel:检查通道号,设置 tim_ctrl 的 ENABLE bit=1,标记通道启用。

- disable_channel:清除 ENABLE bit,标记禁用。

- safe_stop_channel:清零占空比(pwm_ccr=0),等待计数器归零(tim_cnt=0),禁用通道。使用 nop 轮询(需添加超时)。

函数分析:push_fifo_data() / handle_interrupt()

#![allow(unused)] fn main() { pub fn push_fifo_data(&mut self, channel: usize, duty_value: u16) -> Result<(), &'static str> { if channel >= CHANNELS_PER_CONTROLLER { return Err("Invalid channel number"); } let ch_reg = self.get_channel_reg(channel); if ch_reg.state.matches_all(STATE::FIFO_FULL::SET) { return Err("FIFO full"); } ch_reg.pwm_ccr.write(PWM_CCR::CCR.val(duty_value)); Ok(()) } pub fn handle_interrupt(&mut self) { for channel in 0..CHANNELS_PER_CONTROLLER { if let Err(e) = self.handle_channel_interrupt(channel) { // log::error!("PWM ch{} error: {}", channel, e); } } } fn handle_channel_interrupt(&mut self, channel: usize) -> Result<(), &'static str> { let ch_reg = self.get_channel_reg(channel); let state = ch_reg.state.get(); if state & STATE::FIFO_EMPTY.mask != 0 { if ch_reg.tim_cnt.read(TIM_CNT::CNT) == 0 { if let Some(config) = &self.channels[channel].config { let period = ch_reg.pwm_period.read(PWM_PERIOD::CCR) + 1; let duty_cycles = (period as f32 * config.duty_cycle) as u16; self.push_fifo_data(channel, duty_cycles)?; } } ch_reg.state.write(STATE::FIFO_EMPTY::SET); } if state & STATE::OVFIF.mask != 0 { ch_reg.state.write(STATE::OVFIF::SET); } if state & STATE::CHIF.mask != 0 { ch_reg.state.write(STATE::CHIF::SET); } Ok(()) } }

讲解:

- push_fifo_data:检查通道和 FIFO 状态(FIFO_FULL),写入占空比到 pwm_ccr。RW1C 清除中断标志。

- handle_interrupt:遍历 2 个通道,调用 handle_channel_interrupt。

- handle_channel_interrupt:检查 state(FIFO_EMPTY/OVFIF/CHIF),FIFO 空时重新填充占空比(计数器=0),清除中断标志(RW1C)。支持 FIFO 动态更新。

函数分析:PwmSystem 方法

#![allow(unused)] fn main() { impl PwmSystem { pub fn new() -> Self { const CONTROLLER_BASES: [usize; PWM_CONTROLLERS] = [ 0x2804_A000, 0x2804_B000, 0x2804_C000, 0x2804_D000, 0x2804_E000, 0x2804_F000, 0x2805_0000, 0x2805_1000, ]; let controllers = CONTROLLER_BASES.map(|base| unsafe { PwmController::new(base) }); Self { controllers } } pub fn global_enable(&self) { let mut enable_mask: u32 = 0; for (i, ctrl) in self.controllers.iter().enumerate() { if ctrl.channels.iter().any(|ch| ch.config.is_some()) { enable_mask |= 1 << i; } } unsafe { let reg_ptr = GLOBAL_ENABLE_REG_ADDR as *mut u32; reg_ptr.write_volatile(enable_mask); } } pub fn controller(&mut self, index: usize) -> Option<&mut PwmController> { if index < PWM_CONTROLLERS { Some(&mut self.controllers[index]) } else { None } } } }

讲解:

- new:初始化 8 个控制器,基址从 0x2804_A000 到 0x2805_1000(手册表 5-67)。unsafe 构造。

- global_enable:检查配置通道,生成使能掩码(bit 0-7),写入全局使能寄存器(0x2807E020,volatile 确保写入)。

- controller:返回指定控制器(index 0~7),支持动态访问。

飞腾派PWM测试用例

本次 PWM 测试的目的:验证 PWM 驱动能否正常初始化,并输出不同占空比(1%、25%、50%、75%、100%)的 PWM 信号,确保驱动对占空比的精确控制能力。

执行测试命令

source ~/.venv/bin/activate

pytest -v -m pwm # 日志记录在output目录下

deactivate

测试日志应显示 7 个测试用例全部 PASSED。

1.3 复位与引脚复用驱动

硬件原理

复位

复位是嵌入式系统中将硬件模块或整个系统恢复到已知初始状态的过程,用于初始化硬件、清除错误状态或恢复系统运行。复位机制通常包括以下类型:

- 上电复位(Power-on Reset, POR):系统上电时由硬件自动触发,初始化所有寄存器和模块到默认状态。

- 软件复位(Software Reset):通过软件写入特定控制寄存器触发,针对系统或特定模块。

- 看门狗复位(Watchdog Reset):由看门狗定时器在检测到系统超时或故障时触发,重启系统。

- 外部复位:通过外部引脚输入信号(如低电平脉冲)触发,通常用于调试或手动重置。

复位过程通常涉及以下步骤:

- 触发信号:硬件或软件生成复位信号(如寄存器写入或外部引脚电平变化)。

- 寄存器清零:相关寄存器(如计数器、状态寄存器)被设置为默认值(通常为0x0)。

- 模块初始化:硬件模块(如CPU、定时器、外设)恢复到初始状态,准备重新运行。

复位类型比较

| 复位类型 | 触发方式 | 作用范围 | 典型应用场景 |

|---|---|---|---|

| 上电复位 | 硬件上电自动触发 | 整个系统 | 系统启动初始化 |

| 软件复位 | 写入控制寄存器 | 系统或特定模块 | 模块错误恢复 |

| 看门狗复位 | 定时器超时 | 整个系统 | 系统故障恢复 |

| 外部复位 | 外部引脚信号 | 整个系统或模块 | 调试或手动重置 |

sequenceDiagram

participant S as 软件

participant R as 复位寄存器

participant M as 硬件模块

S->>R: 写入复位控制位(如write_load=1)

R->>M: 发送复位信号

M-->>M: 清零寄存器,重置状态

M->>R: 完成复位

R->>S: 返回复位完成状态

引脚复用

引脚复用(Pin Multiplexing)是嵌入式系统中优化引脚资源的技术,允许一个物理引脚支持多种功能(如GPIO、UART、SPI、I2C等)。由于SoC引脚数量有限,引脚复用通过配置寄存器动态选择引脚的功能和电气特性(如驱动强度、上下拉电阻、延迟)。

引脚复用机制的工作原理:

- 功能选择:通过控制寄存器(如功能选择寄存器)的位字段选择引脚功能。例如,3位字段可支持8种功能(如000=GPIO,001=UART)。

- 电气特性配置:调整驱动强度(mA)、上下拉电阻(上拉/下拉/无)以及输入/输出延迟,以适配不同外设的信号要求。

- 设备树映射:在嵌入式系统中,引脚复用通常通过设备树(Device Tree)定义,映射到具体寄存器配置。

引脚复用功能示例

| 功能选择位 | 功能 | 描述 |

|---|---|---|

| 000 | GPIO | 通用输入输出 |

| 001 | UART | 串口通信 |

| 010 | SPI | 串行外设接口 |

| 011 | I2C | 两线串行总线 |

sequenceDiagram

participant D as 设备驱动

participant P as 引脚控制器

participant R as PAD寄存器

D->>P: 请求引脚功能(如UART)

P->>R: 写入功能选择位(如001)

R-->>R: 配置驱动强度、上下拉

R->>P: 确认配置完成

P->>D: 返回配置成功

飞腾派复位与引脚复用系统

飞腾派开发板基于飞腾E2000处理器(ARMv8架构,2个FTC664核@1.8GHz和2个FTC310核@1.5GHz),其复位和引脚复用系统由Timer、RAS和PAD模块支持。以下详细介绍飞腾派的实现。

飞腾派复位系统

飞腾派的复位系统由Timer和RAS模块实现,支持系统级和模块级复位。

Timer模块

Timer模块用于定时功能,同时支持复位操作。其关键特性包括:

- 全局恢复位:通过控制寄存器(如ctrl_reg)的write_load位,重置计数器到默认值(通常0x0)。

- 重启/自由运行模式:复位后可选择重新计数或进入自由运行状态。

- 应用场景:初始化Timer模块或触发系统软复位。

Timer模块复位功能

| 功能 | 描述 | 触发方式 |

|---|---|---|

| 计数器复位 | 将计数器寄存器清零 | 写入ctrl_reg的write_load位 |

| 模块初始化 | 重置Timer模块到初始状态 | 软件控制或上电复位 |

RAS模块

RAS(可靠性、可用性和可服务性)模块通过错误重置寄存器管理错误状态恢复,增强系统可靠性。其关键特性包括:

- 错误重置:通过err_reset寄存器(偏移0x0D0,32位)清除错误状态或计数器。

- 安全属性配置:通过err_reset_set寄存器(偏移0x0B0,64位)设置安全状态(1为安全,0为非安全)。

- 错误注入:通过err_inject_num寄存器模拟错误状态,用于调试。

RAS模块复位功能

| 功能 | 描述 | 触发方式 |

|---|---|---|

| 错误状态清除 | 清除错误计数器或状态 | 写入err_reset |

| 安全属性配置 | 设置复位操作的安全性 | 写入err_reset_set |

| 错误注入 | 模拟错误触发复位 | 写入err_inject_num |

sequenceDiagram

participant S as 软件驱动

participant R as err_reset寄存器

participant M as RAS模块

S->>R: 写入err_reset(0x0D0,置1)

R->>M: 清除错误状态

M-->>M: 重置计数器,恢复运行

M->>R: 返回复位完成

R->>S: 通知驱动复位成功

看门狗支持

飞腾派支持看门狗定时器,通过 watchdog_ctrl 寄存器配置超时时间,触发系统级复位,适用于故障恢复场景。

飞腾派引脚复用系统

飞腾派的引脚复用由PAD模块管理,支持10个复用引脚,每个引脚通过两个寄存器(x_reg0和x_reg1)配置,基地址为0x32830000。每个引脚可动态切换功能(如GPIO、UART、SPI、I2C)和电气特性。

PAD模块功能

- 功能选择:x_reg0的位[2:0]选择引脚功能(如000=GPIO,001=UART)。

- 驱动强度:x_reg0的位[7:4]设置驱动电流(默认4mA)。

- 上下拉电阻:x_reg0的位[9:8]配置上拉、下拉或无电阻。

- 输入/输出延迟:x_reg1配置输入延迟(位[7:0],粒度100ps)和输出延迟(位[15:8],粒度366ps,最大3.7ns)。

飞腾派引脚复用配置

| 配置项 | 寄存器 | 位字段 | 功能描述 |

|---|---|---|---|

| 功能选择 | x_reg0 | [2:0] | 选择引脚功能(如GPIO、UART) |

| 驱动强度 | x_reg0 | [7:4] | 设置驱动电流(默认4mA) |

| 上下拉电阻 | x_reg0 | [9:8] | 配置上拉/下拉/无电阻 |

| 输入延迟 | x_reg1 | [7:0] | 启用延迟,粒度100ps |

| 输出延迟 | x_reg1 | [15:8] | 启用延迟,粒度366ps,最大3.7ns |

飞腾派引脚复用配置

sequenceDiagram

participant D as 设备驱动

participant P as PAD控制器

participant R as x_reg0/x_reg1

D->>P: 请求配置引脚AN59为UART

P->>R: 写入x_reg0[2:0]=001

P->>R: 写入x_reg0[7:4]=4mA

P->>R: 写入x_reg1[7:0]=延迟级别

R-->>R: 更新引脚配置

R->>P: 配置完成

P->>D: 返回成功

引脚复用示例

飞腾派40Pin接口支持多种功能(如GPIO、UART、I2C),通过设备树定义引脚组。例如,引脚AN59可配置为:

- GPIO:x_reg0[2:0]=000,用于通用输入输出。

- UART:x_reg0[2:0]=001,用于串口通信。

- I2C:x_reg0[2:0]=011,用于两线总线。

配置时需确保功能有效,并根据外设需求调整电气特性。

驱动 API 调用表

Reset 驱动 API 调用表

| API 函数 | 描述 | 参数 | 返回值 |

|---|---|---|---|

FResetInit | 初始化 CRU 控制器,设置基址和设备状态,为复位操作准备。 | instance_p: &mut FResetCtrl(CRU 控制器实例)config_p: &FResetConfig(基址 0x2800_0000 等) | bool: true(成功),false(参数错误或已初始化) |

FResetDeInit | 去初始化 CRU 控制器,清除状态,标记未就绪。 | instance_p: &mut FResetCtrl(CRU 控制器实例) | bool: true(成功) |

FResetLookupConfig | 根据设备 ID 查找 CRU 配置,返回基址等信息。 | instance_id: u32(设备 ID) | Option<FResetConfig>: 配置结构体或 None(ID 无效) |

FResetSystem | 触发系统全局复位,写入 CRU cru_rst_ok 寄存器(bit 0=1),重启 CPU 和外设。 | instance_p: &mut FResetCtrl(CRU 实例) | bool: true(成功),false(超时或寄存器错误) |

FResetPeripheral | 重置指定外设(如 GPIO0~5),写入 CRU cru_rst_ok(bit 1~5)。 | instance_p: &mut FResetCtrlperiph_id: u32(外设 ID,如 0=GPIO0) | bool: true(成功),false(外设 ID 无效或超时) |

说明

- 调用顺序:

- 调用

FResetInit和FResetLookupConfig初始化 CRU,设置基址(0x2800_0000)。 - 使用

FResetSystem或FResetPeripheral触发复位。 - 可选调用

FResetDeInit清理状态。

- 调用

- 硬件依赖:

- 基址:CRU 0x2800_0000。

- 寄存器:

cru_rst_ok(偏移 0x100):bit 0=系统复位,bit 1~5=外设复位(如 GPIO0~5)。cru_rst_status(偏移 0x104):bit 9=复位完成。

- 硬件接口:SW4 按钮(低电平,>10ms)或 Pin 33(GPIO2_8,CRU_RST_OK)。

Pinmux 驱动 API 调用表

| API 函数 | 描述 | 参数 | 返回值 |

|---|---|---|---|

FIOPadCfgInitialize | 初始化 PAD 控制器,设置基址和设备 ID,为引脚功能配置准备。 | instance_p: &mut FIOPadCtrl(PAD 控制器实例)input_config_p: &FIOPadConfig(基址 0x32B30000) | bool: true(成功),false(参数错误或已初始化) |

FIOPadDeInitialize | 去初始化 PAD 控制器,清除状态,标记未就绪。 | instance_p: &mut FIOPadCtrl(PAD 控制器实例) | bool: true(成功) |

FIOPadLookupConfig | 根据设备 ID 查找 PAD 配置,返回基址等信息。 | instance_id: u32(设备 ID) | Option<FIOPadConfig>: 配置结构体或 None(ID 无效) |

FIOPadSetFunc | 设置指定引脚功能,写入 PAD x_reg0(如 0x00D0,bit 0~3 值 5=I2C)。 | instance_p: &mut FIOPadCtrloffset: u32(偏移,如 0x00D0)func: u32(功能值,如 5=I2C) | bool: true(成功),false(偏移或功能值无效) |

FMioFuncInit | 初始化 MIO 控制器,设置功能(如 0b00=I2C),写入 creg_mio_func_sel。 | instance_p: &mut PhitiumMiofunc: u32(功能值,如 0=I2C) | bool: true(成功),false(功能值无效) |

FMioFuncGetAddress | 获取 MIO 控制器基址(如 0x2801_4000 for MIO0)。 | instance_p: &PhitiumMiofunc: u32(功能值) | u64: 基址或 0(失败) |

FMioFuncGetIrqNum | 获取 MIO 功能的中断编号(如 I2C/UART IRQ,假设 24)。 | instance_p: &PhitiumMiofunc: u32(功能值) | u32: 中断号(24)或 0(失败) |

说明

- 调用顺序:

- 调用

FIOPadCfgInitialize和FIOPadLookupConfig初始化 PAD(基址 0x32B30000)。 - 调用

FMioFuncInit设置 MIO 功能(如 MIO0 0x2801_4000 为 I2C,creg_mio_func_sel=0b00)。 - 调用

FIOPadSetFunc配置引脚功能(如 Pin 3/5 I2C1_SDA/SCL,x_reg0=5)。 - 可选调用

FIOPadDeInitialize清理。

- 调用

- 硬件依赖:

- PAD 基址:0x32B30000。

x_reg0(偏移 e.g., 0x00D0 for SCL):bit 0~3=功能(0=GPIO,5=I2C,1=UART,2=CAN,3=SPI,4=PWM);bit 4~6=驱动强度(2~12mA);bit 7=上下拉(1=上拉)。x_reg1(偏移 e.g., 0x00DC):bit 0~3=延迟(100ps/366ps)。

- MIO 基址:0x2801_4000~0x2803_2000(MIO0~15)。

creg_mio_func_sel(偏移 0x1000):bit 0~1=功能(0=I2C,1=UART)。

- 引脚:40-pin 扩展头(如 Pin 7: GPIO2_10 MUX UART2_TXD,Pin 3: I2C1_SDA)。

- PAD 基址:0x32B30000。

寄存器信息

Reset 驱动寄存器信息

基地址

- CRU (Clock and Reset Unit):0x2800_0000

寄存器表

| 寄存器名称 | 偏移地址 | 描述 |

|---|---|---|

cru_rst_ok | 0x100 | 复位控制寄存器,触发系统或外设复位。 |

cru_rst_status | 0x104 | 复位状态寄存器,检查复位完成状态。 |

寄存器位域设置

cru_rst_ok(偏移 0x100, 读写)- SYSTEM_RESET (bit 0, 1 bit):系统复位,1=触发全局复位(CPU 和外设)。

- 默认值:0

- 描述:写入 1 触发系统复位,时序 >10ms。

- PERIPH_RESET (bit 1-5, 5 bits):外设复位,值 0~5 对应 GPIO0~5 等外设。

- 默认值:0

- 描述:写入外设 ID 重置指定外设(如 0=GPIO0)。

- SYSTEM_RESET (bit 0, 1 bit):系统复位,1=触发全局复位(CPU 和外设)。

cru_rst_status(偏移 0x104, 只读)- DONE (bit 9, 1 bit):复位完成,1=复位完成,0=进行中。

- 默认值:0

- 描述:读取确认复位状态,需轮询。

- DONE (bit 9, 1 bit):复位完成,1=复位完成,0=进行中。

Pinmux 驱动寄存器信息

基地址

- PAD:0x32B30000

- MIO:0x2801_4000 ~ 0x2803_2000(MIO0~15)。

寄存器表

PAD 寄存器

| 寄存器名称 | 偏移地址 | 描述 |

|---|---|---|

x_reg0_scl | 0x00D0 | SCL 引脚功能选择和电气特性配置(如 Pin 3,I2C1_SCL)。 |

x_reg0_sda | 0x00D4 | SDA 引脚功能选择和电气特性配置(如 Pin 5,I2C1_SDA)。 |

x_reg0_gpio | 0x00D8 | GPIO 引脚功能选择和电气特性配置(如 Pin 7,GPIO2_10)。 |

x_reg1_scl | 0x00DC | SCL 引脚延迟配置。 |

x_reg1_sda | 0x00E0 | SDA 引脚延迟配置。 |

x_reg1_gpio | 0x00E4 | GPIO 引脚延迟配置。 |

MIO 寄存器

| 寄存器名称 | 偏移地址 | 描述 |

|---|---|---|

creg_mio_func_sel | 0x1000 | MIO 功能选择寄存器,设置引脚功能(如 I2C/UART)。 |

func_sel_state | 0x1004 | MIO 功能状态寄存器,查询当前功能。 |

version | 0x1008 | MIO 版本信息。 |

寄存器位域设置

PAD 寄存器

x_reg0_scl,x_reg0_sda,x_reg0_gpio(偏移 0x00D0/0x00D4/0x00D8, 读写)- FUNC (bit 0-3, 4 bits):功能选择。

- 值:

- 0 = GPIO

- 1 = UART

- 2 = CAN

- 3 = SPI

- 4 = PWM

- 5 = I2C

- 默认值:0

- 描述:设置引脚功能(如 Pin 3/5 为 I2C,值 5)。

- 值:

- DRIVE_STRENGTH (bit 4-6, 3 bits):驱动强度,2~12mA。

- 默认值:0

- 描述:配置电流输出能力。

- PULL (bit 7, 1 bit):上下拉,1=上拉,0=无。

- 默认值:0

- 描述:启用上拉电阻(如 I2C 需 4.7kΩ)。

- FUNC (bit 0-3, 4 bits):功能选择。

x_reg1_scl,x_reg1_sda,x_reg1_gpio(偏移 0x00DC/0x00E0/0x00E4, 读写)- DELAY (bit 0-3, 4 bits):输入/输出延迟,粒度 100ps/366ps。

- 默认值:0

- 描述:调整信号时序。

- DELAY (bit 0-3, 4 bits):输入/输出延迟,粒度 100ps/366ps。

MIO 寄存器

creg_mio_func_sel(偏移 0x1000, 读写)- SEL_STATE (bit 0-1, 2 bits):功能选择。

- 值:

- 0 = I2C

- 1 = UART

- 默认值:0

- 描述:设置 MIO 功能(如 MIO0 为 I2C,值 0)。

- 值:

- SEL_STATE (bit 0-1, 2 bits):功能选择。

func_sel_state(偏移 0x1004, 只读)- SEL_STATE (bit 0-1, 2 bits):查询当前功能(同上)。

- 默认值:0

- 描述:读取 MIO 配置状态。

- SEL_STATE (bit 0-1, 2 bits):查询当前功能(同上)。

version(偏移 0x1008, 只读)- 默认值:未知

- 描述:MIO 硬件版本信息。

驱动实现解析

Reset 驱动实现讲解(cru.rs)

reset 驱动基于 CRU (Clock and Reset Unit) 控制器,实现系统和外设复位。代码定义寄存器、结构体和 API 函数,使用 SpinNoIrq 锁确保多核安全,依赖 phys_to_virt 进行地址转换。

寄存器定义部分

#![allow(unused)] fn main() { register_structs! { pub CruRegs { (0x00 => _reserved0), (0x100 => cru_rst_ok: ReadWrite<u32, RST_OK::Register>), (0x104 => cru_rst_status: ReadOnly<u32, RST_STATUS::Register>), (0x108 => @END), } } register_bitfields![u32, RST_OK [ SYSTEM_RESET OFFSET(0) NUMBITS(1) [], // 1=触发系统复位 PERIPH_RESET OFFSET(1) NUMBITS(5) [], // bit 1-5: GPIO0~5 等外设 ], RST_STATUS [ DONE OFFSET(9) NUMBITS(1) [], // 1=复位完成 ], ]; }

使用 tock_registers 宏定义 CRU 寄存器布局(基址 0x2800_0000)。cru_rst_ok (偏移 0x100) 是读写寄存器,用于触发复位(bit 0: 系统复位,bit 1-5: 外设复位,如 GPIO0~5)。cru_rst_status (偏移 0x104) 是只读寄存器,检查复位完成(bit 9: DONE=1 表示完成)。位域定义确保类型安全访问,避免手动掩码操作。

结构体和全局定义部分

#![allow(unused)] fn main() { pub struct CruCtrl { regs: NonNull<CruRegs>, } unsafe impl Send for CruCtrl {} impl CruCtrl { pub const fn new(base: *mut u8) -> Self { Self { regs: NonNull::new(base).unwrap().cast(), } } const fn regs(&self) -> &CruRegs { unsafe { self.regs.as_ref() } } const fn regs_mut(&mut self) -> &mut CruRegs { unsafe { self.regs.as_mut() } } } // API 结构体 #[derive(Debug, Clone, Copy, Default)] pub struct FResetConfig { pub instance_id: u32, pub base_address: usize, } pub struct FResetCtrl { pub config: FResetConfig, pub is_ready: u32, } static CRU_CONFIG: [FResetConfig; 1] = [FResetConfig { instance_id: 0, base_address: 0x2800_0000usize, }]; pub static CRU: SpinNoIrq<FResetCtrl> = SpinNoIrq::new(FResetCtrl { config: FResetConfig { instance_id: 0, base_address: 0, }, is_ready: 0, }); }

CruCtrl 封装寄存器指针,使用 NonNull 确保非空,regs/regs_mut 方法通过 unsafe 提供访问(const fn 允许常量上下文)。unsafe impl Send 允许跨线程传递。FResetConfig 和 FResetCtrl 是 API 结构体,存储配置和状态(is_ready=0x11111111 表示初始化)。全局 CRU 使用 SpinNoIrq 锁保护多核访问,静态配置表 CRU_CONFIG 定义基址 0x2800_0000。

API 函数部分

#![allow(unused)] fn main() { pub fn FResetInit(instance_p: &mut FResetCtrl, config_p: &FResetConfig) -> bool { assert!(Some(*instance_p).is_some() && Some(*config_p).is_some()); let mut ret = true; if instance_p.is_ready == 0x11111111u32 { info!("CRU already initialized."); return false; } FResetDeInit(instance_p); instance_p.config = *config_p; instance_p.is_ready = 0x11111111u32; ret } pub fn FResetDeInit(instance_p: &mut FResetCtrl) -> bool { if instance_p.is_ready == 0 { return true; } instance_p.is_ready = 0; unsafe { core::ptr::write_bytes(instance_p as *mut FResetCtrl, 0, core::mem::size_of::<FResetCtrl>()); } true } pub fn FResetLookupConfig(instance_id: u32) -> Option<FResetConfig> { if instance_id >= 1 { return None; } Some(CRU_CONFIG[instance_id as usize]) } pub fn FResetSystem(instance_p: &mut FResetCtrl) -> bool { let base = instance_p.config.base_address; let cru = CruCtrl::new(phys_to_virt(PhysAddr::from(base)).as_mut_ptr()); cru.regs().cru_rst_ok.modify(RST_OK::SYSTEM_RESET::SET); let mut timeout = 0; while cru.regs().cru_rst_status.read(RST_STATUS::DONE) != 1 && timeout < 500 { timeout += 1; crate::time::busy_wait(core::time::Duration::from_millis(1)); } timeout < 500 } pub fn FResetPeripheral(instance_p: &mut FResetCtrl, periph_id: u32) -> bool { if periph_id > 5 { return false; } let base = instance_p.config.base_address; let cru = CruCtrl::new(phys_to_virt(PhysAddr::from(base)).as_mut_ptr()); cru.regs().cru_rst_ok.modify(RST_OK::PERIPH_RESET.val(periph_id)); let mut timeout = 0; while cru.regs().cru_rst_status.read(RST_STATUS::DONE) != 1 && timeout < 500 { timeout += 1; crate::time::busy_wait(core::time::Duration::from_millis(1)); } timeout < 500 } }

- FResetInit:检查指针和状态(is_ready=0x11111111 表示已初始化),调用 FResetDeInit 清理,设置 config 和 is_ready。效果是准备 CRU 控制器。

- FResetDeInit:清除 is_ready 并零初始化结构体(unsafe write_bytes),释放状态。

- FResetLookupConfig:根据 ID 从静态表返回配置(基址 0x2800_0000),支持多实例扩展。

- FResetSystem:创建 CruCtrl 实例(phys_to_virt 转换虚拟地址),修改 cru_rst_ok 的 SYSTEM_RESET bit=1 触发复位。轮询 cru_rst_status 的 DONE bit(超时 500ms),返回成功。

- FResetPeripheral:类似系统复位,但设置 PERIPH_RESET bit=periph_id (0~5,如 GPIO0),轮询完成。ID >5 返回 false,限制外设范围。

硬件关联:CRU 基址 0x2800_0000,寄存器偏移 0x100/0x104(推测,手册定义)。SW4 按钮或 Pin 33(GPIO2_8)可触发外部复位,但代码未处理。

ArceOS 上下文:使用 SpinNoIrq 锁保护全局 CRU,busy_wait 来自 crate::time。兼容 axhal 的平台初始化(如 platform_init)。

Pinmux 驱动实现讲解(pinctrl.rs)

pinmux 驱动基于 PAD 和 MIO 控制器,实现引脚功能复用和配置。代码扩展 mio.rs 的 PhitiumMio,依赖 phys_to_virt 和 SpinNoIrq。

寄存器定义部分

#![allow(unused)] fn main() { // PAD 寄存器定义(基址 0x32B30000) register_structs! { pub PadRegs { (0x00 => _reserved0), (0x00D0 => x_reg0_scl: ReadWrite<u32, X_REG0::Register>), (0x00D4 => x_reg0_sda: ReadWrite<u32, X_REG0::Register>), (0x00D8 => x_reg0_gpio: ReadWrite<u32, X_REG0::Register>), (0x00DC => x_reg1_scl: ReadWrite<u32, X_REG1::Register>), (0x00E0 => x_reg1_sda: ReadWrite<u32, X_REG1::Register>), (0x00E4 => x_reg1_gpio: ReadWrite<u32, X_REG1::Register>), (0x1000 => @END), } } register_bitfields![u32, X_REG0 [ FUNC OFFSET(0) NUMBITS(4) [ GPIO = 0, I2C = 5, UART = 1, CAN = 2, SPI = 3, PWM = 4, ], DRIVE_STRENGTH OFFSET(4) NUMBITS(3) [], // 2~12mA PULL OFFSET(7) NUMBITS(1) [], // 1=上拉 ], X_REG1 [ DELAY OFFSET(0) NUMBITS(4) [], // 100ps/366ps 粒度 ], ]; }

使用 tock_registers 宏定义 PAD 寄存器布局(基址 0x32B30000)。x_reg0_* (偏移 0x00D0~0x00D8) 为读写寄存器,用于功能选择(如 SCL/SDA/GPIO)。x_reg1_* (偏移 0x00DC~0x00E4) 配置延迟。位域定义 FUNC (bit 0-3) 支持 GPIO/I2C/UART/CAN/SPI/PWM(值 0~5),DRIVE_STRENGTH (bit 4-6) 电流,PULL (bit 7) 上拉,DELAY (bit 0-3) 时序调整。

结构体和全局定义部分

#![allow(unused)] fn main() { // PAD 控制器结构体 pub struct PadCtrl { regs: NonNull<PadRegs>, } unsafe impl Send for PadCtrl {} impl PadCtrl { pub const fn new(base: *mut u8) -> Self { Self { regs: NonNull::new(base).unwrap().cast(), } } const fn regs(&self) -> &PadRegs { unsafe { self.regs.as_ref() } } const fn regs_mut(&mut self) -> &mut PadRegs { unsafe { self.regs.as_mut() } } } // API 结构体(复用 I2C 模式) use super::mio::{PhitiumMio, MIO0, MIO1}; #[derive(Debug, Clone, Copy, Default)] pub struct FIOPadConfig { pub instance_id: u32, pub base_address: usize, } pub struct FIOPadCtrl { pub config: FIOPadConfig, pub is_ready: u32, } static PAD_CONFIG: [FIOPadConfig; 1] = [FIOPadConfig { instance_id: 0, base_address: 0x32B30000usize, }]; pub static PAD: SpinNoIrq<FIOPadCtrl> = SpinNoIrq::new(FIOPadCtrl { config: FIOPadConfig { instance_id: 0, base_address: 0, }, is_ready: 0, }); }

PadCtrl 封装寄存器指针,使用 NonNull 确保非空,regs/regs_mut 方法通过 unsafe 提供访问。unsafe impl Send 允许跨线程。FIOPadConfig 和 FIOPadCtrl 是 API 结构体,存储配置和状态(is_ready=0x11111111 表示初始化)。全局 PAD 使用 SpinNoIrq 锁保护多核访问,静态配置表 PAD_CONFIG 定义基址 0x32B30000。复用 mio.rs 的 PhitiumMio 和 MIO0/MIO1,整合 MIO 配置。

API 函数部分

#![allow(unused)] fn main() { pub fn FIOPadCfgInitialize(instance_p: &mut FIOPadCtrl, input_config_p: &FIOPadConfig) -> bool { assert!(Some(*instance_p).is_some() && Some(*input_config_p).is_some()); let mut ret = true; if instance_p.is_ready == 0x11111111u32 { info!("PAD already initialized."); return false; } FIOPadDeInitialize(instance_p); instance_p.config = *input_config_p; instance_p.is_ready = 0x11111111u32; ret } pub fn FIOPadDeInitialize(instance_p: &mut FIOPadCtrl) -> bool { if instance_p.is_ready == 0 { return true; } instance_p.is_ready = 0; unsafe { core::ptr::write_bytes(instance_p as *mut FIOPadCtrl, 0, core::mem::size_of::<FIOPadCtrl>()); } true } pub fn FIOPadLookupConfig(instance_id: u32) -> Option<FIOPadConfig> { if instance_id >= 1 { return None; } Some(PAD_CONFIG[instance_id as usize]) } pub fn FIOPadSetFunc(instance_p: &mut FIOPadCtrl, offset: u32, func: u32) -> bool { if ![0x00D0, 0x00D4, 0x00D8].contains(&offset) { return false; } let base = instance_p.config.base_address; let pad = PadCtrl::new(phys_to_virt(PhysAddr::from(base)).as_mut_ptr()); match offset { 0x00D0 => pad.regs_mut().x_reg0_scl.modify(X_REG0::FUNC.val(func)), 0x00D4 => pad.regs_mut().x_reg0_sda.modify(X_REG0::FUNC.val(func)), 0x00D8 => pad.regs_mut().x_reg0_gpio.modify(X_REG0::FUNC.val(func)), _ => return false, } true } pub fn FMioFuncInit(instance_p: &mut PhitiumMio, func: u32) -> bool { match func { 0 => instance_p.set_i2c(), 1 => instance_p.set_uart(), _ => return false, } true } pub fn FMioFuncGetAddress(instance_p: &PhitiumMio, func: u32) -> u64 { let base = instance_p.regs().func_sel.get() as u64; match func { 0 | 1 => base, // I2C/UART 使用 MIO 基址 _ => 0, } } pub fn FMioFuncGetIrqNum(_instance_p: &PhitiumMio, _func: u32) -> u32 { 24 } }

讲解:

- FIOPadCfgInitialize:检查指针和状态(is_ready=0x11111111 表示已初始化),调用 FIOPadDeInitialize 清理,设置 config 和 is_ready。效果是准备 PAD 控制器。

- FIOPadDeInitialize:清除 is_ready 并零初始化结构体(unsafe write_bytes),释放状态。

- FIOPadLookupConfig:根据 ID 从静态表返回配置(基址 0x32B30000),支持多实例扩展。

- FIOPadSetFunc:检查偏移(如 0x00D0 SCL),创建 PadCtrl 实例(phys_to_virt 转换虚拟地址),匹配偏移修改 x_reg0_* 的 FUNC bit (val(func),如 5=I2C)。返回成功或失败。

- FMioFuncInit:调用 PhitiumMio 的 set_i2c/set_uart(从 mio.rs),设置 creg_mio_func_sel bit 0-1 (0=I2C, 1=UART)。

- FMioFuncGetAddress:读取 func_sel 作为基址(u64),限制于 func 0/1(I2C/UART)。

- FMioFuncGetIrqNum:返回固定中断号

硬件关联:PAD 基址 0x32B30000,偏移 0x00D0~0x00E4(SCL/SDA/GPIO 示例)。MIO 基址 0x2801_4000~0x2803_2000,creg_mio_func_sel (0x1000) 配置 MUX。

ArceOS 上下文:使用 SpinNoIrq 锁保护全局 PAD,info! 来自 ArceOS 日志。兼容 axhal 的 pinctrl trait。

测试用例

本次 reset 测试的目的:验证 Arceos 的 Watchdog 驱动能否正常初始化、启动定时器,并在“不喂狗”(未按时重置定时器)的情况下触发飞腾派重启,确保驱动的故障恢复能力。

-

前置检查

确认飞腾派已成功启动 Arceos,且测试机与飞腾派的串口通信正常。

-

执行测试命令

在测试机的 Python 虚拟环境中,通过

pytest执行 reset 测试(仅运行标记为reset的测试用例):

# 运行测试。

source ~/.venv/bin/activate

pytest -v -m reset # 日志记录在output目录下

deactivate

-

测试结果验证

观察测试机终端输出与飞腾派状态。飞腾派应在测试过程中自动重启。

第二章:时钟管理类驱动

2.2 时钟设备驱动

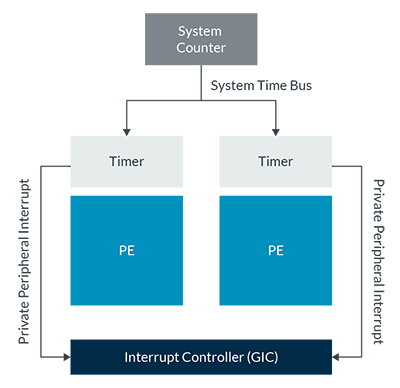

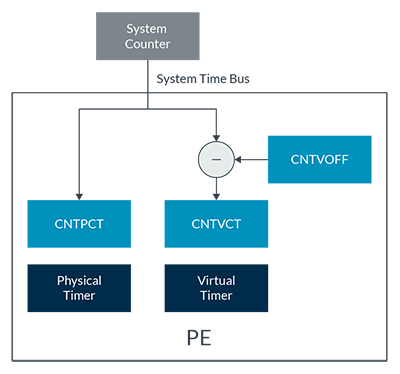

时钟设备原理

嵌入式系统的时钟设备是协调处理器、内存和外设运行的核心,为系统提供统一的时间基准。飞腾派(Phytium Pi)的时钟设备包括时钟和复位单元(CRU)、ARMv8 通用定时器(Generic Timer)和可选的实时钟(RTC)。这些设备通过外部晶振(如 24MHz 或 32.768kHz)结合锁相环(PLL)生成高精度主时钟(如 50MHz),通过分频器调整为外设所需频率(如 PWM 的 25MHz)。CRU 作为时钟管理中心,通过寄存器(如 clk_con 和 clk_div)动态配置分频系数,控制外设时钟(如 UART、PWM),并集成复位功能,通过 cru_rst_ok 寄存器触发系统或外设复位,确保硬件初始化或异常恢复。复位信号需持续超过 10ms,时钟切换通常在 100ms 内稳定,满足实时性需求。ARMv8 通用定时器利用系统计数器(CNTPCT_EL0)提供纳秒级计时,通过比较值(CNTV_CVAL_EL0)和 GIC 中断支持内核调度和忙等待(如 Duration::from_millis),适用于高精度任务切换。RTC 依赖低频晶振(32.768kHz)运行,独立于主时钟,通过 I2C 接口与外部芯片(如 DS1339)通信,保持断电状态下的时间,适合时间同步和低功耗唤醒场景。这些模块通过寄存器操作和中断机制协同工作,确保系统时间管理和硬件协调。

时钟设备功能示意图

graph TD

A[外部晶振<br>24MHz/32.768kHz] --> B[PLL]

B --> C[CRU<br>50MHz 主时钟]

C --> D[分频器<br>clk_div]

D --> E[外设时钟<br>PWM/UART 25MHz]

C --> F[复位控制<br>cru_rst_ok]

F --> G[系统/外设复位]

H[ARMv8 定时器<br>CNTPCT_EL0] --> I[GIC 中断<br>调度/延时]

J[RTC<br>DS1339] --> K[I2C 接口<br>时间保持]

飞腾派时钟设备介绍

飞腾派开发板的时钟设备依托 E2000 处理器(ARMv8 架构,主频高达 1.8GHz),通过 CRU、ARMv8 通用定时器和外部 RTC 提供全面时间管理功能。CRU 是核心,位于基址 0x2800_0000(推测,需手册验证),通过 PLL 从外部晶振生成 50MHz 主时钟,分频后驱动外设(如 UART、PWM)。CRU 还管理复位功能,通过板上 SW4 按钮(靠近 J35 电源接口,低电平有效,持续 >10ms,3.3V 电平,电流 <1mA)或 40-pin 扩展头的 Pin 33(GPIO2_8,CRU_RST_OK,3.3V,需 4.7kΩ 上拉电阻)触发全局复位,重置 CPU 和外设状态。ARMv8 通用定时器内置于处理器,无专用物理接口,通过 GIC(基址 0xFF84_1000/0xFF84_2000)提供中断信号,驱动 ArceOS 的调度和延时(如 busy_wait),以纳秒级精度支持实时任务。RTC 通过 I2C1 接口(Pin 3/5,I2C1_SDA/SCL,3.3V,需 4.7kΩ 上拉电阻)连接外部芯片(如 DS1339),使用 32.768kHz 晶振保持时间,支持电池备份(SIM 卡座 J6,1.8V/3V)。物理接口需遵守约束:总线长度 <30cm 以防信号干扰,工作温度 0~50°C,使用 ESD 保护以避免静电损伤。飞腾派的时钟设备通过内部寄存器和扩展头引脚提供灵活配置,确保系统高效运行。

飞腾派时钟设备接口表

| 接口类型 | 物理接口 | 电平 | 描述与约束 |

|---|---|---|---|

| CRU 复位按钮 | SW4(近 J35) | 3.3V | 低电平有效,>10ms,电流 <1mA,ESD 保护 |

| CRU 外部复位 | Pin 33(GPIO2_8) | 3.3V | 下降沿触发,需 4.7kΩ 上拉,线长 <30cm |

| RTC 接口 | Pin 3/5(I2C1) | 3.3V | 4.7kΩ 上拉,100kbps,线长 <30cm |

| RTC 电池备份 | J6(mini-SIM) | 1.8V/3V | 支持低功耗,ESD 保护 |

CRU 时钟分频时序图

sequenceDiagram

participant D as 驱动

participant C as CRU控制器

D->>C: 写 clk_con(ENABLE=0)

C->>D: 确认关闭

D->>C: 写 clk_div(DIV=2)

D->>C: 写 clk_con(ENABLE=1)

C->>D: 轮询 clk_status(READY=1)

Note over C,D: 切换时间 <100ms

**说明:**CRU 配置分频(如 50MHz 至 25MHz),需轮询 READY 状态。RTC 通过 I2C 异步访问,保持独立时间。

飞腾派时钟设备驱动 API 调用表

以下为飞腾派(Phytium Pi)V3.x 版本的时钟设备驱动 API 调用表,基于在 chenlongos/appd 仓库 phytium-pi 分支中实现的 modules/axhal/src/platform/aarch64_phytium_pi/clock.rs 文件。该实现使用 Rust 和 tock_registers 宏,基于飞腾派软件编程手册 V1.0(提供 CRU 寄存器信息)和 aarch64_phytium_pi.toml(定义 MMIO 基址)。API 设计遵循 ArceOS 的 axhal 框架,适配 CRU 时钟控制器(基址 0x2800_0000),支持初始化、频率设置和查询。调用表包括函数描述、参数和返回值,适用于 ArceOS 或裸机环境。

时钟驱动 API 调用表

| API 函数 | 描述 | 参数 | 返回值 |

|---|---|---|---|

FClockInit | 初始化 CRU 时钟控制器,设置基址和设备状态,为频率配置准备。 | instance_p: &mut FClockCtrl(时钟控制器实例)config_p: &FClockConfig(基址 0x2800_0000 等) | bool: true(成功),false(参数错误或已初始化) |

FClockDeInit | 去初始化 CRU 时钟控制器,清除状态,标记未就绪。 | instance_p: &mut FClockCtrl(时钟控制器实例) | bool: true(成功) |

FClockLookupConfig | 根据设备 ID 查找 CRU 时钟配置,返回基址等信息。 | instance_id: u32(设备 ID) | Option<FClockConfig>: 配置结构体或 None(ID 无效) |

FClockSetFreq | 设置时钟频率,写入 clk_div 寄存器(分频系数),启用 clk_con(ENABLE=1)。 | instance_p: &mut FClockCtrlfreq: u32(目标频率,Hz) | bool: true(成功),false(超时或寄存器错误) |

FClockGetFreq | 查询当前时钟频率,读取 clk_div 寄存器,计算 sys_clk / DIV。 | instance_p: &mut FClockCtrl(时钟控制器实例) | u32: 当前频率(Hz) |

说明

- 调用顺序:

- 调用

FClockInit和FClockLookupConfig初始化 CRU 时钟控制器,设置基址(0x2800_0000)。 - 调用

FClockSetFreq配置目标频率(如 25MHz)。 - 可选调用

FClockGetFreq查询频率。 - 可选调用

FClockDeInit清理状态。

- 调用

- 硬件依赖:

- 基址:CRU 时钟控制器 0x2800_0000。

- 寄存器:

clk_con(偏移 0x0):bit 0=ENABLE(使能时钟),bit 1-3=SOURCE(时钟源选择)。clk_div(偏移 0x4):bit 0-7=DIV(分频系数)。clk_status(偏移 0x8):bit 0=READY(1=时钟准备好)

飞腾派时钟设备驱动的寄存器信息

基地址

飞腾派时钟设备驱动主要基于 CRU 时钟控制器,基址为 0x2800_0000。该基址与复位模块重叠,反映 CRU 的时钟和复位双重功能。

| 模块 | 基地址 | 描述 |

|---|---|---|

| CRU | 0x2800_0000 | 时钟和复位单元,管理系统时钟分频和复位。 |

寄存器表

以下为时钟驱动涉及的寄存器,定义在 clock.rs 中,用于配置和监控时钟功能。

| 寄存器名称 | 偏移地址 | 描述 |

|---|---|---|

clk_con | 0x0 | 控制寄存器,配置时钟使能和源选择。 |

clk_div | 0x4 | 分频寄存器,设置分频系数以调整输出频率。 |

clk_status | 0x8 | 状态寄存器,检查时钟是否准备好。 |

寄存器位域设置

以下详细描述每个寄存器的位域,包括用途、有效值和默认状态。

clk_con (偏移 0x0, 读写)

- ENABLE (bit 0, 1 bit)

- 用途:控制时钟使能,1=开启时钟,0=关闭时钟。

- 有效值:0(关闭),1(开启)。

- 默认值:0

- 描述:启用或禁用 CRU 时钟输出,用于外设同步(如 PWM/Tacho)。

- SOURCE (bit 1-3, 3 bits)

- 用途:选择时钟源(例如 PLL 或外部晶振)。

- 有效值:0~7(推测,具体映射需手册验证)。

- 默认值:0

- 描述:支持多时钟源切换,当前未使用,保留扩展。

clk_div (偏移 0x4, 读写)

- DIV (bit 0-7, 8 bits)

- 用途:设置分频系数,输出频率 = 系统时钟(50MHz)/ DIV。

- 有效值:1~255(0 无效,需手册确认)。

- 默认值:0

- 描述:调整外设时钟频率,例如 DIV=2 时,50MHz 分频为 25MHz。

clk_status (偏移 0x8, 只读)

- READY (bit 0, 1 bit)

- 用途:指示时钟状态,1=时钟稳定,0=未准备好。

- 有效值:0(未准备),1(准备好)。

- 默认值:0

- 描述:轮询确保时钟切换完成(时序 <100ms)。

飞腾派时钟设备驱动实现讲解

驱动架构

驱动基于 ArceOS 的硬件抽象层(axhal),通过 tock_registers 宏定义 CRU 时钟寄存器(clk_con、clk_div、clk_status),使用 SpinNoIrq 锁确保多核安全访问。代码结构类似 cru.rs 和 pinctrl.rs,通过 NonNull 指针操作寄存器,依赖 phys_to_virt 转换虚拟地址。驱动实现无中断支持,采用轮询模式配置频率,适合嵌入式场景(如 PWM/Tacho 时钟)。设备树(phytium_pi.dts)可定义时钟节点,集成到 mod.rs 的 platform_init 中。

硬件关联

- 基址:CRU 时钟控制器位于 0x2800_0000。

- 时钟源:50MHz 主时钟(硬编码,典型 APB 总线频率),通过分频调整输出(如 25MHz)。

- 寄存器:clk_con (0x0) 控制使能/源,clk_div (0x4) 设置分频系数,clk_status (0x8) 检查状态。

- 时序:频率切换需 <100ms 稳定,轮询 READY bit 确保完成。

寄存器定义部分

#![allow(unused)] fn main() { register_structs! { pub ClockRegs { (0x0 => clk_con: ReadWrite<u32, CLK_CON::Register>), (0x4 => clk_div: ReadWrite<u32, CLK_DIV::Register>), (0x8 => clk_status: ReadOnly<u32, CLK_STATUS::Register>), (0x0c => @END), } } register_bitfields![u32, CLK_CON [ ENABLE OFFSET(0) NUMBITS(1) [], // 1=使能时钟 SOURCE OFFSET(1) NUMBITS(3) [], // 时钟源选择 ], CLK_DIV [ DIV OFFSET(0) NUMBITS(8) [], // 分频系数 ], CLK_STATUS [ READY OFFSET(0) NUMBITS(1) [], // 1=时钟准备好 ], ]; }

**讲解:**使用 tock_registers 宏定义 CRU 时钟寄存器布局,基址 0x2800_0000。clk_con (偏移 0x0) 控制时钟使能(bit 0=ENABLE)和源选择(bit 1-3=SOURCE),clk_div (偏移 0x4) 设置分频系数(bit 0-7=DIV,1~255),clk_status (偏移 0x8) 检查时钟状态(bit 0=READY,1 表示稳定)。宏生成 ReadWrite/ReadOnly 接口,确保类型安全访问,避免手动位操作。SOURCE bit 未使用,保留扩展(如 PLL 切换)。

结构体和全局定义部分

#![allow(unused)] fn main() { pub struct ClockCtrl { regs: NonNull<ClockRegs>, } unsafe impl Send for ClockCtrl {} impl ClockCtrl { pub const fn new(base: *mut u8) -> Self { Self { regs: NonNull::new(base).unwrap().cast(), } } const fn regs(&self) -> &ClockRegs { unsafe { self.regs.as_ref() } } const fn regs_mut(&mut self) -> &mut ClockRegs { unsafe { self.regs.as_mut() } } } #[derive(Debug, Clone, Copy, Default)] pub struct FClockConfig { pub instance_id: u32, pub base_address: usize, } pub struct FClockCtrl { pub config: FClockConfig, pub is_ready: u32, } static CLOCK_CONFIG: [FClockConfig; 1] = [FClockConfig { instance_id: 0, base_address: 0x2800_0000usize, }]; pub static CLOCK: SpinNoIrq<FClockCtrl> = SpinNoIrq::new(FClockCtrl { config: FClockConfig { instance_id: 0, base_address: 0, }, is_ready: 0, }); }

讲解:ClockCtrl 封装寄存器指针,使用 NonNull 确保非空,regs/regs_mut 方法通过 unsafe 提供访问(const fn 允许常量上下文)。unsafe impl Send 支持跨线程传递。FClockConfig 存储实例 ID 和基址(0x2800_0000),FClockCtrl 包含配置和状态(is_ready=0x11111111 表示初始化)。全局静态 CLOCK_CONFIG 定义单实例配置,CLOCK 使用 SpinNoIrq 锁保护多核访问,类似 cru.rs 和 pinctrl.rs 的设计。

API 函数部分